74ABT541 データシートの表示(PDF) - Fairchild Semiconductor

部品番号

コンポーネント説明

メーカー

74ABT541 Datasheet PDF : 12 Pages

| |||

74ABT541

Octal Buffer/Line Driver with 3-STATE Outputs

March 2007

tm

Features

■ Non-inverting buffers

■ Output sink capability of 64mA, source capability of

32mA

■ Guaranteed output skew

■ Guaranteed multiple output switching specifications

■ Output switching specified for both 50pF and 250pF

loads

■ Guaranteed simultaneous switching, noise level and

dynamic threshold performance

■ Guaranteed latchup protection

■ High-impedance, glitch-free bus loading during entire

power up and power down cycle

■ Nondestructive, hot-insertion capability

■ Flow-through pinout for ease of PC board layout

■ Disable time less than enable time to avoid bus

contention

General Description

The ABT541 is an octal buffer and line driver with

3-STATE outputs designed to be employed as a memory

and address driver, clock driver, or bus-oriented trans-

mitter/receiver. The ABT541 is similar to the ABT244

with broadside pinout.

Ordering Information

Order Number

74ABT541CSC

74ABT541CSJ

74ABT541CMSA

74ABT541CMTC

Package

Number

M20B

M20D

MSA20

MTC20

Package Description

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide

20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

20-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm Wide

20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153,

4.4mm Wide

Devices also available in Tape and Reel. Specify by appending suffix “X” to the ordering number.

Pb-Free package per JEDEC J-STD-020B.

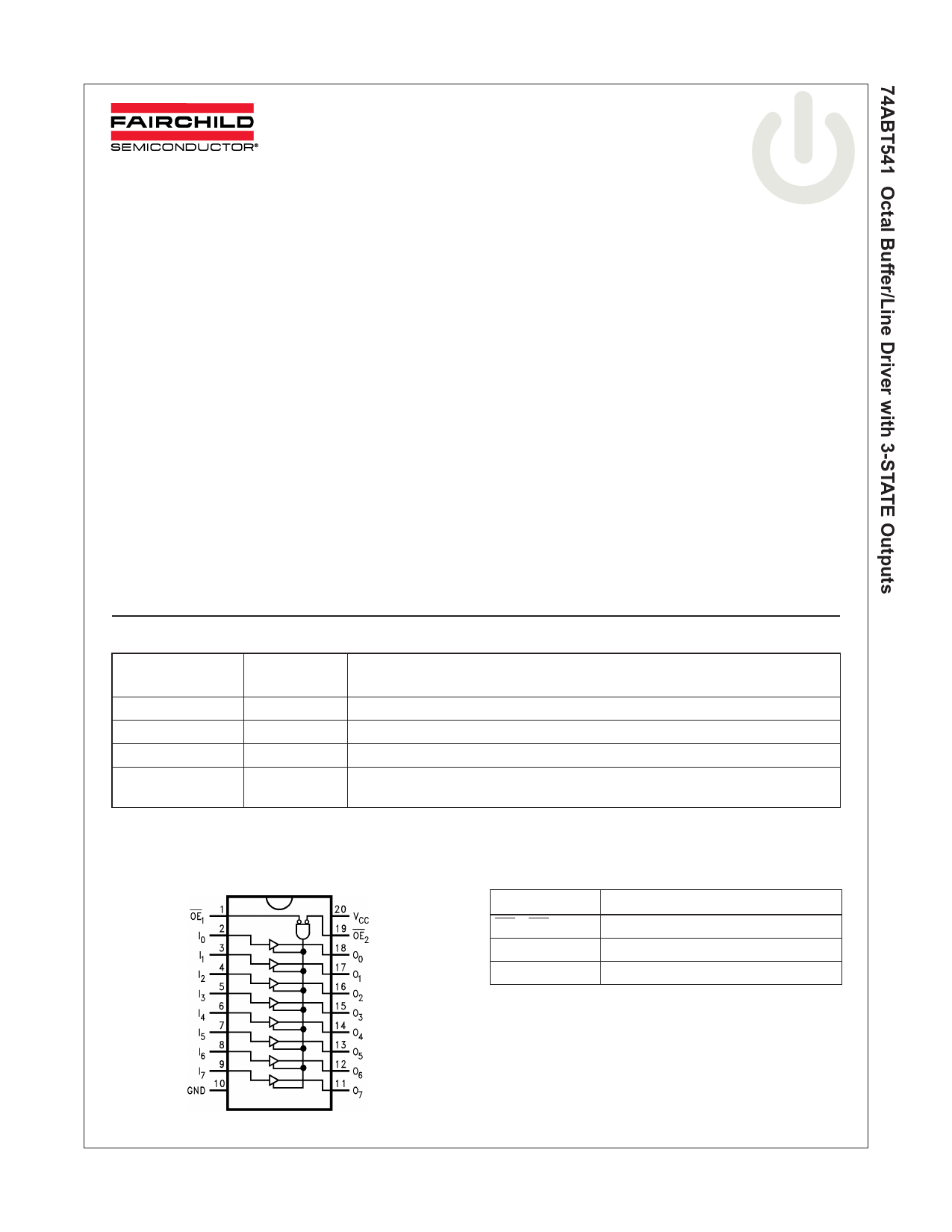

Connection Diagram

Pin Descriptions

Pin Names

OE1, OE2

I0–I7

O0–O7

Description

Output Enable Input (Active LOW)

Inputs

Outputs

©1992 Fairchild Semiconductor Corporation

74ABT541 Rev. 1.4

www.fairchildsemi.com