AD9923ABBCZRL データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

AD9923ABBCZRL Datasheet PDF : 84 Pages

| |||

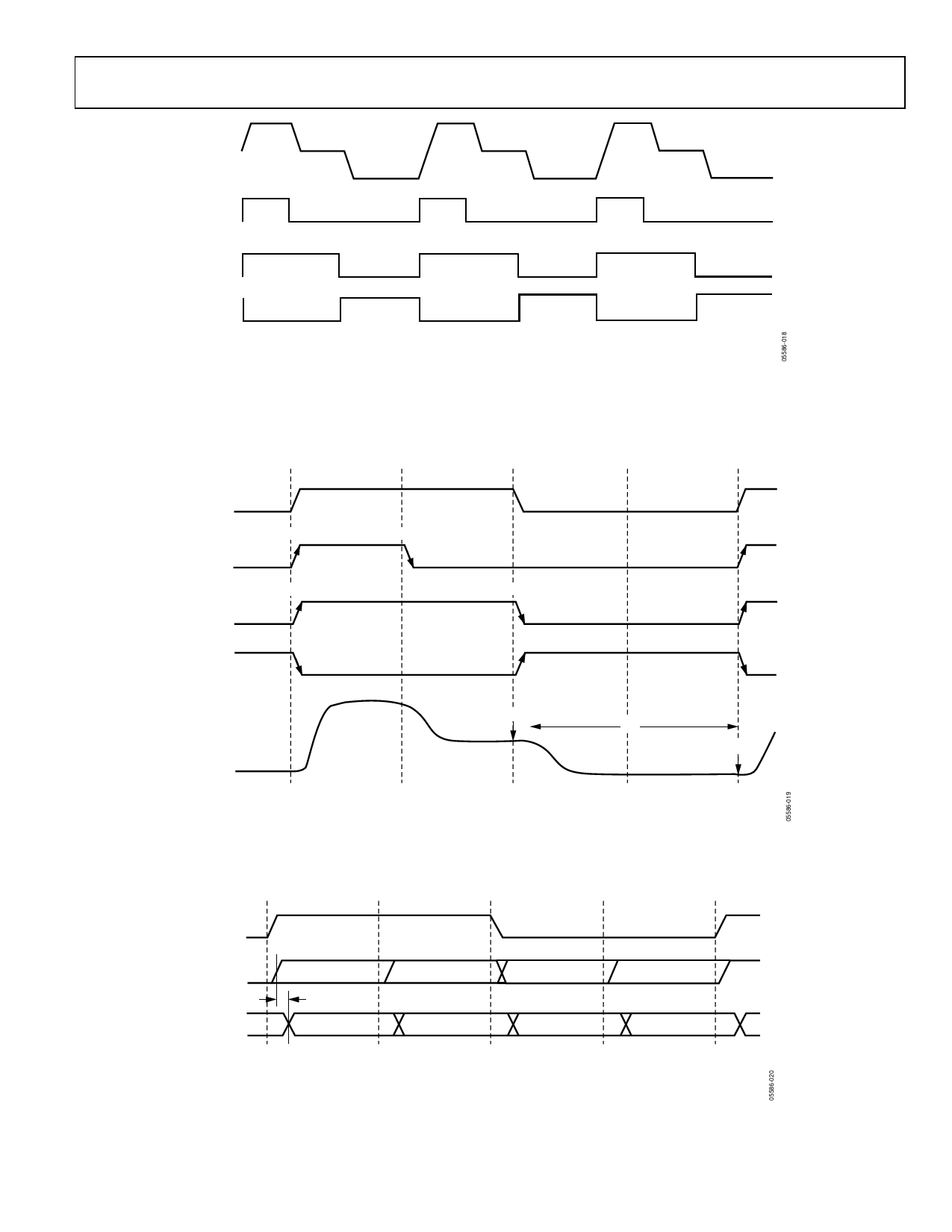

CCD

SIGNAL

RG

HL/H1/H3

H2/H4

NOTES

1. USING THE SAME TOGGLE POSITIONS FOR H1 AND H3 GENERATES STANDARD 2-PHASE H-CLOCKING.

Figure 19. 2-Phase H-Clock Operation

AD9923A

POSITION

PIXEL

PERIOD

RG

HL/H1/H3

P[0]

RGr[0]

Hr[0]

P[12]

RGf[12]

P[24]

Hf[24]

P[36]

P[48] = P[0]

H2/H4

CCD

SIGNAL

SHP[24]

tS1

SHD[48]

NOTES

1. ALL SIGNAL EDGES ARE FULLY PROGRAMMABLE TO ANY OF THE 48 POSITIONS WITHIN ONE PIXEL PERIOD.

2. DEFAULT POSITIONS FOR EACH SIGNAL ARE SHOWN.

Figure 20. High Speed Timing Default Locations

P[0]

PIXEL

PERIOD

P[12]

P[24]

P[36]

P[48] = P[0]

DCLK

tOD

DOUT

NOTES

1. DATA OUTPUT (DOUT) AND DCLK PHASE ARE ADJUSTABLE WITH RESPECT TO THE PIXEL PERIOD.

2. WITHIN 1 CLOCK PERIOD, THE DATA TRANSITION CAN BE PROGRAMMED TO 48 DIFFERENT LOCATIONS.

3. OUTPUT DELAY (tOD) FROM DCLK RISING EDGE TO DOUT RISING EDGE IS PROGRAMMABLE.

Figure 21. Digital Output Phase Adjustment

Rev. A | Page 17 of 84