TC820CKW データシートの表示(PDF) - Microchip Technology

部品番号

コンポーネント説明

メーカー

TC820CKW Datasheet PDF : 28 Pages

| |||

TC820

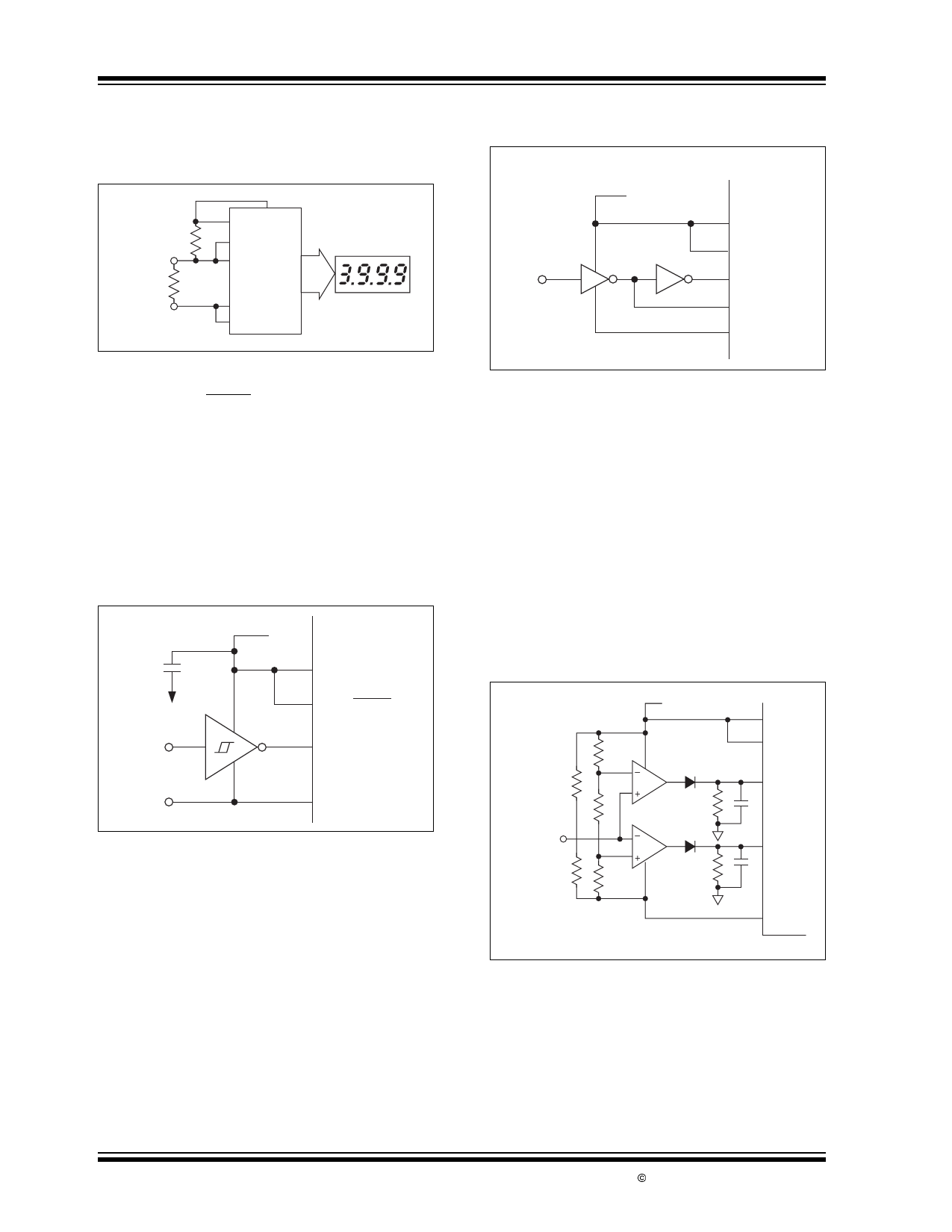

FIGURE 5-8:

RSTANDARD

RUNKNOWN

LOW PARTS COUNT

RATIOMETRIC

RESISTANCE

MEASUREMENT

VDD

VREF+

VREF-

VIN+

TC820

VIN-

Analog

Common

LCD

5.9 Buffering the FREQ Input

When the FREQ/VOLTS input is high and the LOGIC

input is low, the TC820 will count pulses at the RANGE/

FREQ input. The time-base will be FOSC/40,000, or

1 second with a 40kHz clock. The signal to be mea-

sured should swing from VDD to DGND. The RANGE/

FREQ input has CMOS input levels without hysteresis.

For best results, especially with low frequency sine-

wave inputs, an external buffer with hysteresis should

be added. A typical circuit is shown in Figure 5-9.

FIGURE 5-9:

FREQUENCY COUNTER

EXTERNAL BUFFER

+

1µF

DGND

Frequency

Input

GND

+9V

TC820

VDD

FREQ/VOLTS

74HC14

RANGE/FREQ

DGND

5.10 Logic Probe Inputs

The DP0/LO and DP1/HI inputs provide the logic probe

inputs when the LOGIC input is high. Driving either

DP0/LO or DP1/HI to a logic high will turn on the appro-

priate LCD annunciator. When DP0/LO is high, the

buzzer will be on.

To provide a "single input" logic probe function, external

buffers should be used. A simple circuit is shown in

Figure 5-10. This circuit will turn the appropriate annun-

ciator on for high and low level inputs.

FIGURE 5-10:

Logic

Probe

Input

*

SIMPLE EXTERNAL

LOGIC PROBE BUFFER

TC820

+9V

*

*74HC14

VDD

LOGIC

DP1/HI

DP0/LO

DGND

If carefully controlled logic thresholds are required, a

window comparator can be used. Figure 5-11 shows a

typical circuit. This circuit will turn on the high or low

annunciators when the logic thresholds are exceeded,

but the resistors connected from DP0/LO and DP1/HI

to DGND will turn both annunciators off when the logic

probe is unconnected.

The TC820 logic inputs are not latched internally, so

pulses of short duration will usually be difficult or impos-

sible to see. To display short pulses properly, the input

pulse should be "stretched." The circuit of Figure 5-11

shows capacitors added across the input pull-down

resistors to stretch the input pulse and permit viewing

short duration input pulses.

FIGURE 5-11:

WINDOW COMPARATOR

LOGIC PROBE

1MΩ

Logic

Probe Input

1MΩ

+9V

R1

VH –

+

R2

–

VL +

R3

TC820

1N4148

1N4148

VDD

LOGIC

DP1/HI

DP0/LO

DGND

Note: Select R1, R2, R3 for desired logic thresholds.

DS21476B-page 20

© 2002 Microchip Technology Inc.