M50LPW080N データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

M50LPW080N Datasheet PDF : 44 Pages

| |||

M50LPW080

A10), data signals, (DQ0-DQ7) and three control

signals (RC, G, W). An additional signal, RP, can

be used to reset the memory.

The Address/Address Multiplexed (A/A Mux) Inter-

face is included for use by Flash Programming

equipment for faster factory programming. Only a

subset of the features available to the Low Pin

Count (LPC) Interface are available; these include

all the Commands but exclude the Security fea-

tures and other registers.

The following operations can be performed using

the appropriate bus cycles: Bus Read, Bus Write,

Output Disable and Reset.

When the Address/Address Multiplexed (A/A Mux)

Interface is selected all the blocks are unprotect-

ed. It is not possible to protect any blocks through

this interface.

Bus Read. Bus Read operations are used to out-

put the contents of the Memory Array, the Elec-

tronic Signature and the Status Register. A valid

Bus Read operation begins by latching the Row

Address and Column Address signals into the

memory using the Address Inputs, A0-A10, and

the Row/Column Address Select RC. Then Write

Enable (W) and Interface Reset (RP) must be

High, VIH, and Output Enable, G, Low, VIL, in order

to perform a Bus Read operation. The Data Inputs/

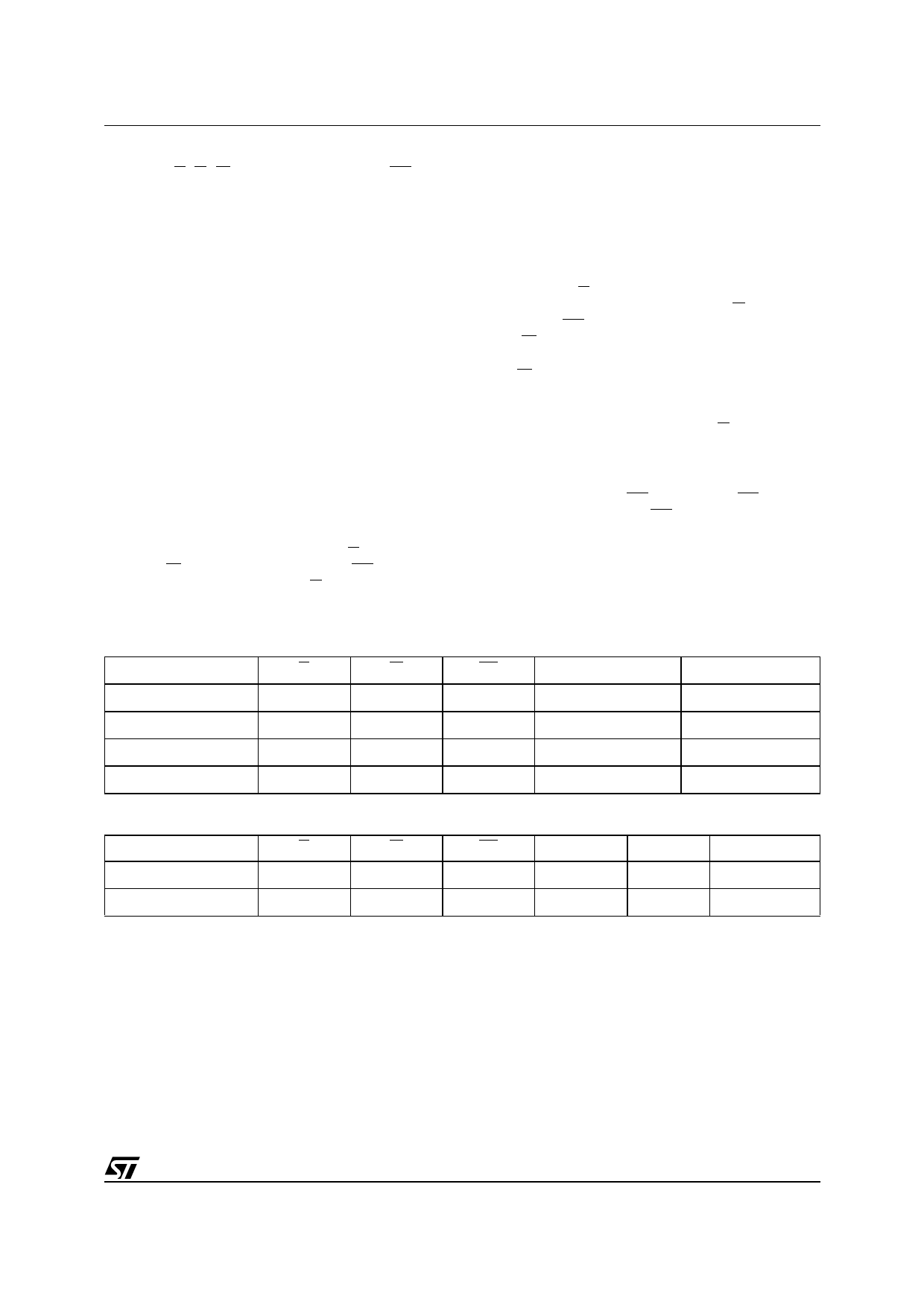

Table 5. A/A Mux Bus Operations

Operation

G

Bus Read

VIL

Bus Write

VIH

Output Disable

VIH

Reset

VIL or VIH

W

VIH

VIL

VIH

VIL or VIH

Outputs will output the value, see Figure 13. and

Table 25. for details of when the output becomes

valid.

Bus Write. Bus Write operations write to the

Command Interface. A valid Bus Write operation

begins by latching the Row Address and Column

Address signals into the memory using the Ad-

dress Inputs, A0-A10, and the Row/Column Ad-

dress Select RC. The data should be set up on the

Data Inputs/Outputs; Output Enable, G, and Inter-

face Reset, RP, must be High, VIH and Write En-

able, W, must be Low, VIL. The Data Inputs/

Outputs are latched on the rising edge of Write En-

able, W. See Figure 14. and Table 26. for details

of the timing requirements.

Output Disable. The data outputs are high-im-

pedance when the Output Enable, G, is at VIH.

Reset. During Reset mode all internal circuits are

switched off, the memory is deselected and the

outputs are put in high-impedance. The memory is

in Reset mode when RP is Low, VIL. RP must be

held Low, VIL for tPLPH. If RP is goes Low, VIL, dur-

ing a Program or Erase operation, the operation is

aborted and the memory cells affected no longer

contain valid data; the memory can take up to tPL-

RH to abort a Program or Erase operation.

RP

VPP

DQ7-DQ0

VIH

Don’t Care

Data Output

VIH

VCC or VPPH

Data Input

VIH

Don’t Care

Hi-Z

VIL

Don’t Care

Hi-Z

Table 6. Manufacturer and Device Codes

Operation

G

W

Manufacturer Code

VIL

VIH

Device Code

VIL

VIH

RP

A19-A1

A0

DQ7-DQ0

VIH

VIL

VIL

20h

VIH

VIL

VIH

2Fh

13/44