M58MR016ZC-T データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

M58MR016ZC-T Datasheet PDF : 51 Pages

| |||

M58MR016C, M58MR016D

POWER CONSUMPTION

Power-down

The memory provides Reset/Power-down control

input RP. The Power-down function can be acti-

vated only if the relevant Read Configuration Reg-

ister bit is set to ’1’. In this case, when the RP

signal is pulled at VSS the supply current drops to

typically ICC2 (see Table 26), the memory is dese-

lected and the outputs are in high impedance. If

RP is pulled to VSS during a Program or Erase op-

eration, this operation is aborted and the memory

content is no longer valid (see Reset/Power-down

input description).

Power-up

The memory Command Interface is reset on Pow-

er-up to Read Array. Either E or W must be tied to

VIH during Power-up to allow maximum security

and the possibility to write a command on the first

rising edge of W. At Power-up the device is config-

ured as:

– Page mode: (CR15 = 1)

– Power-down disabled: (CR10 = 0)

– BINV disabled: (CR14 = 0).

All blocks are protected and unlocked.

VDD, VDDQ and VPP are independent power sup-

plies and can be biased in any order.

Supply Rails

Normal precautions must be taken for supply volt-

age decoupling; each device in a system should

have the VDD rails decoupled with a 0.1µF capac-

itor close to the VDD, VDDQ and VSS pins. The PCB

trace widths should be sufficient to carry the re-

quired VDD program and erase currents.

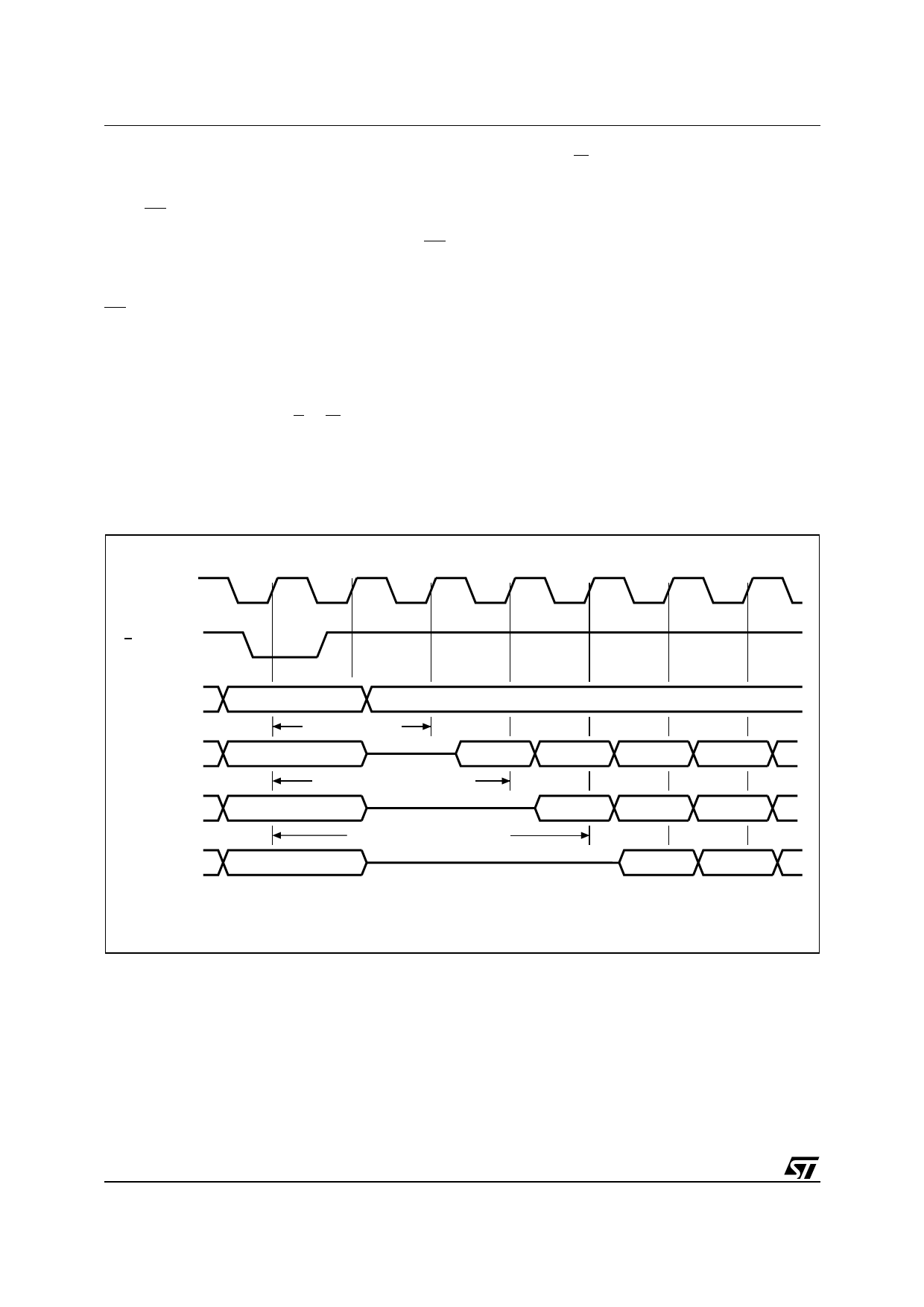

Figure 6. X-Latency Configuration Sequence

K

L

A19-A16

ADQ15-ADQ0

ADQ15-ADQ0

ADQ15-ADQ0

VALID ADDRESS

CONF. CODE 2

VALID ADDRESS

VALID DATA VALID DATA VALID DATA VALID DATA

CONFIGURATION CODE 3

VALID ADDRESS

VALID DATA VALID DATA VALID DATA

CONFIGURATION CODE 4

VALID ADDRESS

VALID DATA VALID DATA

AI05233

20/51