MF0064M-07AT データシートの表示(PDF) - Mitsumi

部品番号

コンポーネント説明

メーカー

MF0064M-07AT Datasheet PDF : 32 Pages

| |||

MITSUBISHI STORAGE CARD

Preliminary

ATA PC CARDS

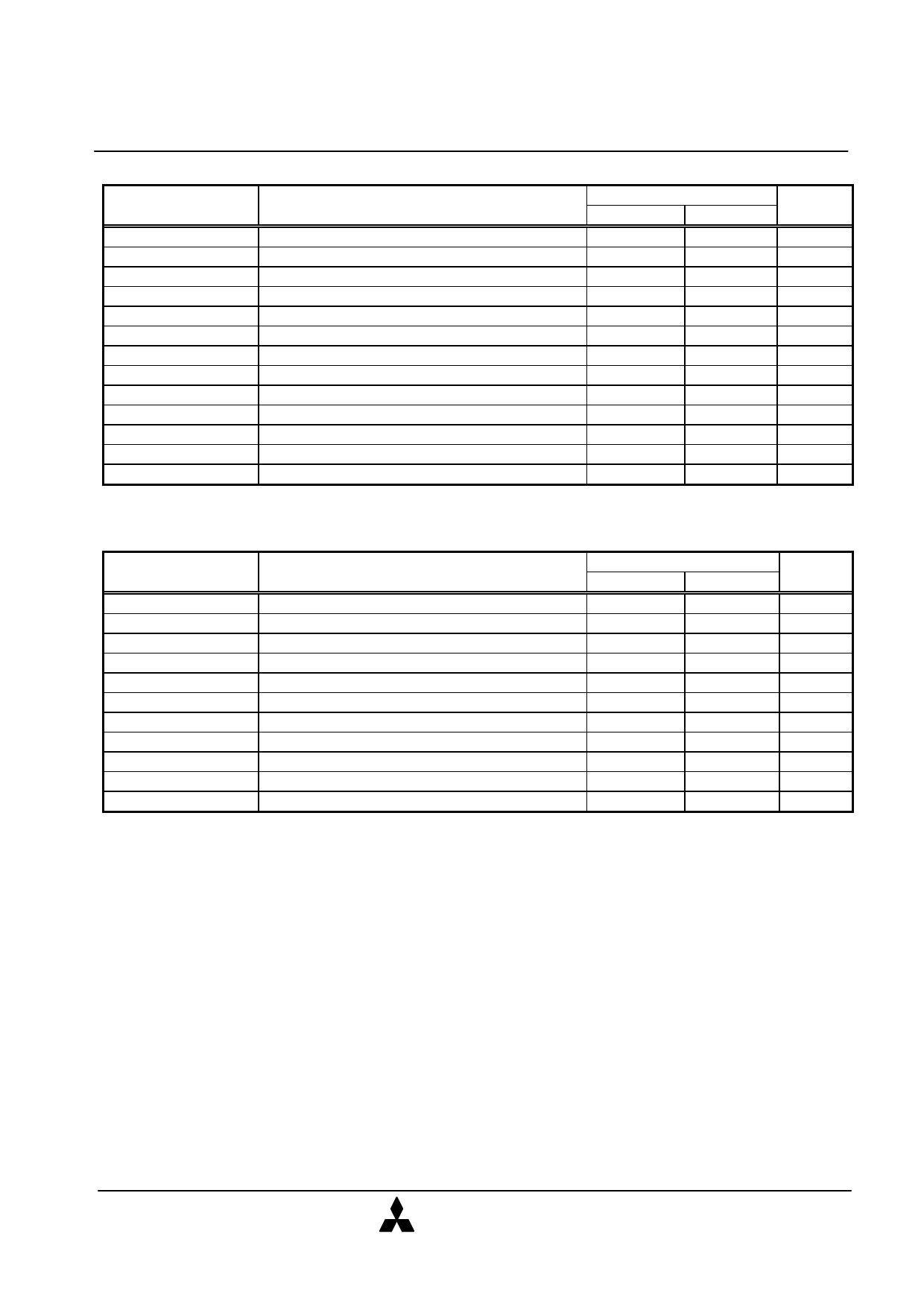

I/O READ (INPUT) TIMING

Limit

Symbol

Parameter

Min

Max

Unit

td(IORD)

Data Delay after IORD#

100

ns

th(IORD)

Data Hold following IORD#

0

ns

tw(IORD)

IORD# Width Time

165

ns

tsuA(IORD)

Address Setup before IORD#

70

ns

thA(IORD)

Address Hold following IORD#

20

ns

tsuCE(IORD)

CE# Setup before IORD#

5

ns

thCE(IORD)

CE# Hold following IORD#

20

ns

tsuREG(IORD)

REG# Setup before IORD#

5

ns

thREG(IORD)

REG# Hold following IORD#

0

ns

tdfINPACK(IORD)

INPACK# Delay Falling from IORD#

0

45

ns

tdrINPACK(IORD)

INPACK# Delay Rising from IORD#

45

ns

tdfIOIS16(ADR)

IOIS16# Delay Falling from Address

35

ns

tdrIOIS16(ADR)

IOIS16# Delay Rising from Address

35

ns

The maximum load on INPACK# and IOIS16# are 1 LSTTL with 50 pF total load.

I/O WRITE (OUTPUT) TIMING

Symbol

Parameter

Limit

Min

Max

Unit

tsu(IOWR)

Data Setup before IOWR#

60

ns

th(IOWR)

Data Hold following IOWR#

30

ns

tw(IOWR)

IOWR# Width Time

165

ns

tsuA(IOWR)

Address Setup before IOWR#

70

ns

thA(IOWR)

Address Hold following IOWR#

20

ns

tsuCE(IOWR)

CE# Setup before IOWR#

5

ns

thCE(IOWR)

CE# Hold following IOWR#

20

ns

tsuREG(IOWR)

REG# Setup before IOWR#

5

ns

thREG(IOWR)

REG# Hold following IOWR#

0

ns

tdfIOIS16(ADR)

IOIS16# Delay Falling from Address

35

ns

tdrIOIS16(ADR)

IOIS16# Delay Rising from Address

35

ns

The maximum load on INPACK# and IOIS16# are 1 LSTTL with 50 pF total load.

MITSUBISHI

ELECTRIC

26

Oct.1999 Rev. 0.2