M80C186 データシートの表示(PDF) - Intel

部品番号

コンポーネント説明

メーカー

M80C186 Datasheet PDF : 59 Pages

| |||

M80C186

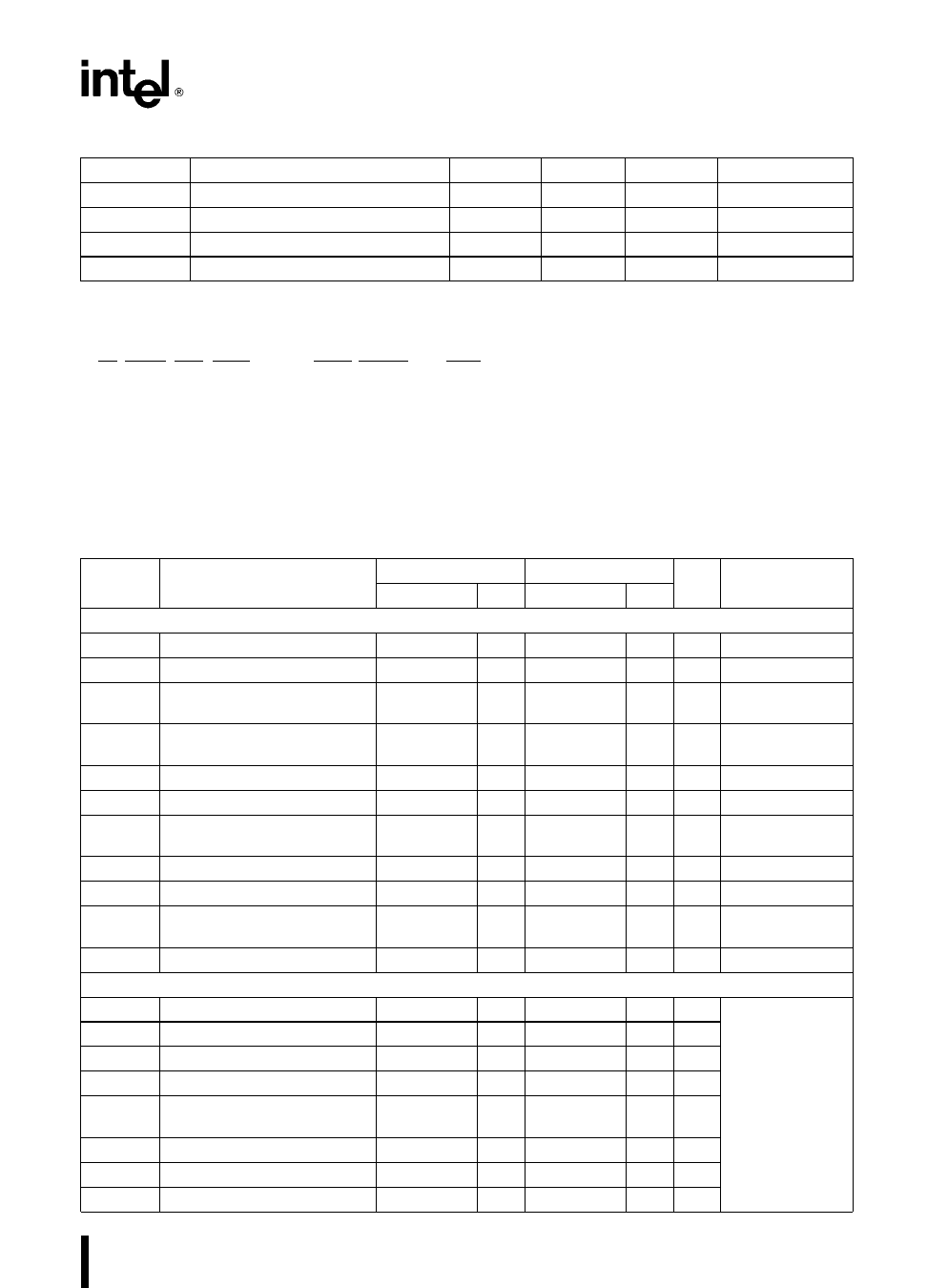

DC CHARACTERISTICS (Over Specified Operating Conditions) (Continued)

Symbol

Parameter

Min

Max

Units

VCLI

VCHI

CIN

CIO

Clock Input Low Voltage (X1)

b0 5

06

V

Clock Input High Voltage (X1)

39

VCC

V

Input Capacitance

10

pF

I O Capacitance

20

pF

Comments

1 MHz(2)

1 MHz(2)

NOTES

1 Pins being floated during HOLD or by invoking the ONCE Mode

2 Characterization conditions are a) Frequency e 1 MHz b) Unmeasured pins at GND VIN at a5 0V or a0 45V

3 Current is measured with the device in RESET with X1 and X2 driven and all other non-power pins open

4 RD QSMD UCS MSC0 PEREQ MCSL ERROR and TEST BUSY pins have internal pullup devices that are active at

RESET Excessive loading on these pins can cause the M80C186 to go into undesired modes of operation (e g Queue

Status ONCE) upon RESET

PIN TIMINGS

AC CHARACTERISTICS (Over Specified Operating Conditions)

All timings are measured at 1 5V and 100 pF loading on CLKOUT unless otherwise noted

All output test conditions are with CL e 50 – 200 pF (10 MHz) and CL e 50 – 100 pF (12 5 MHz)

For AC tests input VIL e 0 45V and VIN e 2 4V except at X1 where VIH e VCC b 0 5V

Symbol

Parameter

M80C186-10

Min

Max

M80C186-12

Unit

Min

Max

Comments

M80C186 TIMING REQUIREMENTS

TDVCL Data In Setup (A D)

20

TCLDX Data In Hold (A D)

5

TARYCH ARDY Resolution

20

Transition Setup Time(1)

20

ns

5

ns

20

ns

TARYLCL Asynchronous Ready

30

(ARDY) Setup Time

30

ns

TCLARX ARDY Active Hold Time

15

TARYCHL ARDY Inactive Hold Time

15

TSRYCL Synchronous Ready (SRDY)

20

Transition Setup Time

15

ns

15

ns

20

ns

TCLSRY SRDY Transition Hold Time

20

THVCL

HOLD Setup(1)

20

TINVCH INTR NMI TEST TMR IN

20

Setup Time(1)

20

ns

20

ns

20

ns

TINVCL DRQ0 DRQ1 Setup Time(1)

20

20

ns

M80C186 MASTER INTERFACE TIMING RESPONSES

TCLAV

TCLAX

TCLAZ

TCHCZ

TCHCV

TLHLL

TCHLH

TCHLL

Address Valid Delay

5

50

5

37

Address Hold

0

0

Address Float Delay

TCLAX

30

TCLAX

25

Command Lines Float Delay

40

33

Command Lines Valid

Delay (after Float)

45

37

ALE Width (min)

ALE Active Delay

TCLCL b 30

TCLCL b 30

30

25

ALE Inactive Delay

30

25

ns

ns CL e

ns

50 pF – 200 pF

all outputs

ns (except TCLTMV)

ns

10 MHz

CL e

ns 50 pF – 100 pF

ns

all outputs

12 5 MHz

ns

45