TMP86C829B データシートの表示(PDF) - Toshiba

部品番号

コンポーネント説明

メーカー

TMP86C829B Datasheet PDF : 160 Pages

| |||

TMP86C820FG

2. Operational Description

2.1 CPU Core Functions

The CPU core consists of a CPU, a system clock controller, and an interrupt controller.

This section provides a description of the CPU core, the program memory, the data memory, and the reset circuit.

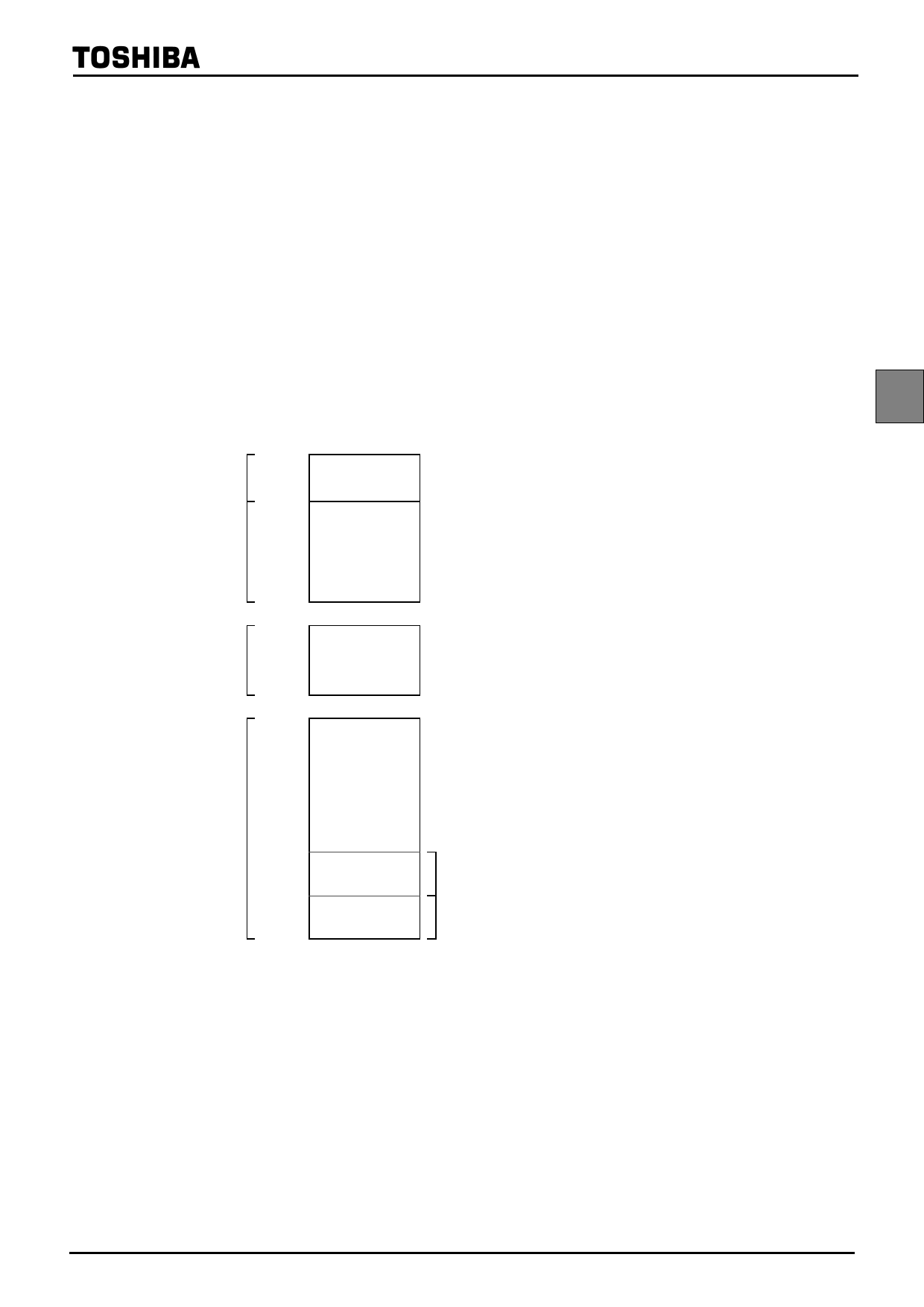

2.1.1 Memory Address Map

The TMP86C820FG memory is composed MaskROM, RAM, DBR(Data buffer register) and SFR(Special

function register). They are all mapped in 64-Kbyte address space. Figure 2-1 shows the TMP86C820FG

memory address map.

SFR

0000H

003FH

0040H

RAM

013FH

DBR

0F80H

0FFFH

E000H

64 bytes

256

bytes

128

bytes

SFR:

RAM:

Special function register includes:

I/O ports

Peripheral control registers

Peripheral status registers

System control registers

Program status word

Random access memory includes:

Data memory

Stack

DBR:

Data buffer register includes:

Peripheral control registers

Peripheral status registers

LCD display memory

MaskROM: Program memory

MaskROM

FFC0H

FFDFH

FFE0H

FFFFH

8192

bytes

Vector table for vector call instructions

(32 bytes)

Vector table for interrupts

(32 bytes)

Figure 2-1 Memory Address Map

2.1.2 Program Memory (MaskROM)

The TMP86C820FG has a 8192 bytes (Address E000H to FFFFH) of program memory (MaskROM ).

2.1.3 Data Memory (RAM)

The TMP86C820FG has 256bytes (Address 0040H to 013FH) of internal RAM. The first 192 bytes (0040H

to 00FFH) of the internal RAM are located in the direct area; instructions with shorten operations are available

against such an area.

Page 9