Q67120-C1050 データシートの表示(PDF) - Siemens AG

部品番号

コンポーネント説明

メーカー

Q67120-C1050 Datasheet PDF : 49 Pages

| |||

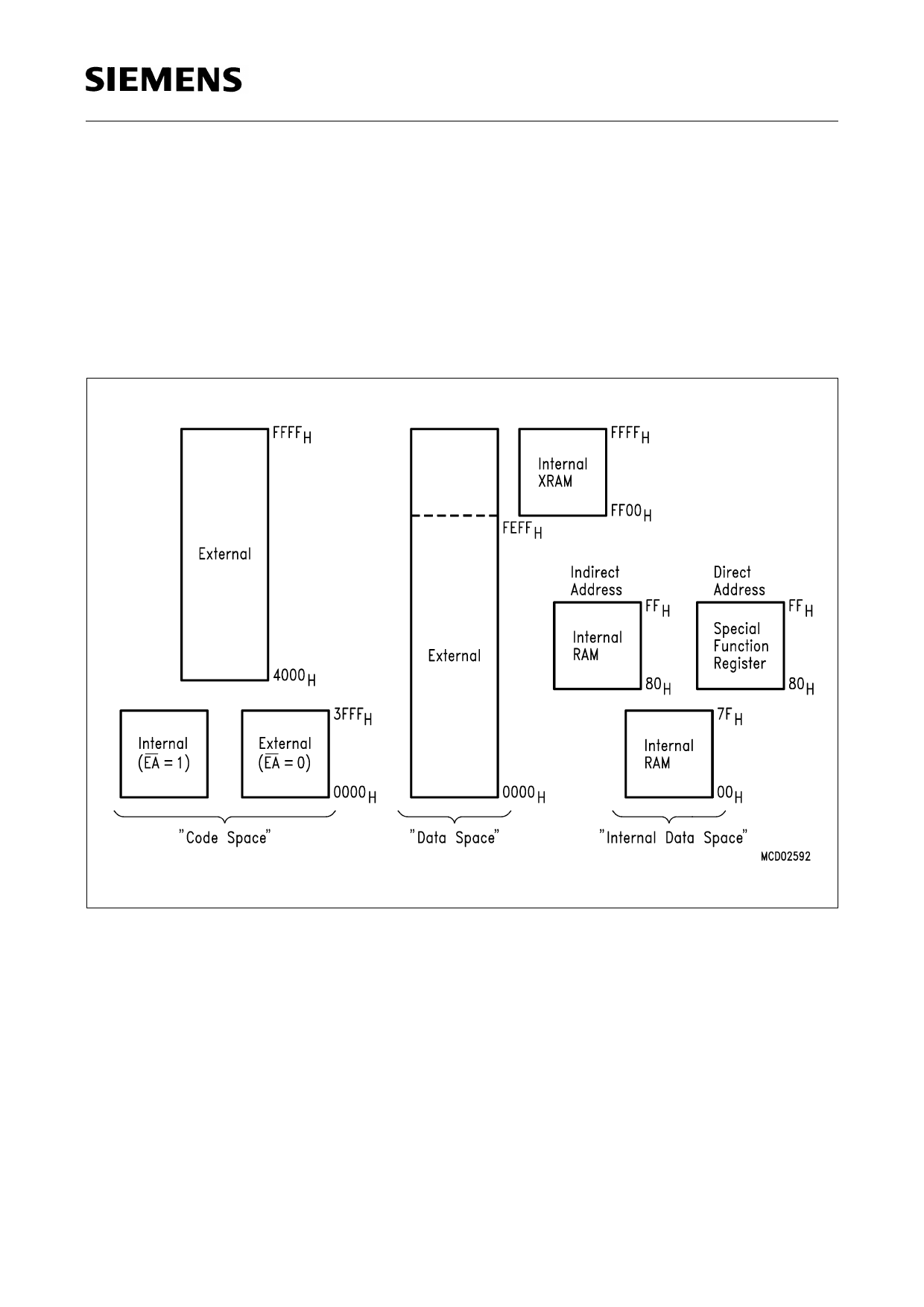

Memory Organization

The C504 CPU manipulates operands in the following four address spaces:

– up to 64 Kbyte of external program memory

– up to 64 Kbyte of external data memory

– 256 bytes of internal data memory

– 256 bytes of internal XRAM data memory

– a 128 byte special function register area

Figure 4 illustrates the memory address spaces of the C504.

C504

Figure 4

C504 Memory Map

The XRAM in the C504 is a memory area that is logically located at the upper end of the external

memory space, but is integrated on the chip. Because the XRAM is used in the same way as

external data memory the same instruction types (MOVX instructions) must be used for accessing

the XRAM. The XRAM can be enabled and disabled by the XMAP bit in the SYSCON register.

ROM Protection

The C504-2R ROM version allows to protect the content of the internal ROM against read out by

non authorized people. The type of ROM protection (protected or unprotected) is fixed with the

ROM mask. Therefore, the customer of a C504-2R ROM version has to define whether ROM

protection has to be selected or not.

Semiconductor Group

13