FM24CL64B(2014) гғҮгғјгӮҝгӮ·гғјгғҲгҒ®иЎЁзӨәпјҲPDFпјү - Cypress Semiconductor

йғЁе“Ғз•ӘеҸ·

гӮігғігғқгғјгғҚгғігғҲиӘ¬жҳҺ

гғЎгғјгӮ«гғј

FM24CL64B Datasheet PDF : 19 Pages

| |||

FM24CL64B

AC Switching Characteristics

Over the Operating Range

Parameter[5]

Alt.

Parameter

Description

fSCL[6]

SCL clock frequency

tSU; STA

Start condition setup for repeated Start

tHD;STA

Start condition hold time

tLOW

Clock LOW period

tHIGH

Clock HIGH period

tSU;DAT

tSU;DATA Data in setup

tHD;DAT

tHD;DATA Data in hold

tDH

Data output hold (from SCL @ VIL)

tR[7]

tr

Input rise time

tF[7]

tf

Input fall time

tSU;STO

STOP condition setup

tAA

tVD;DATA SCL LOW to SDA Data Out Valid

tBUF

Bus free before new transmission

tSP

Noise suppression time constant on SCL, SDA

Min Max Min

вҖ“ 0.1 вҖ“

4.7 вҖ“ 0.6

4.0 вҖ“ 0.6

4.7 вҖ“ 1.3

4.0 вҖ“ 0.6

250 вҖ“ 100

0

вҖ“

0

0

вҖ“

0

вҖ“ 1000 вҖ“

вҖ“ 300 вҖ“

4.0 вҖ“ 0.6

вҖ“

3

вҖ“

4.7 вҖ“ 1.3

вҖ“

50

вҖ“

Max

0.4

вҖ“

вҖ“

вҖ“

вҖ“

вҖ“

вҖ“

вҖ“

300

300

вҖ“

0.9

вҖ“

50

Min

вҖ“

0.25

0.25

0.6

0.4

100

0

0

вҖ“

вҖ“

0.25

вҖ“

0.5

вҖ“

Max Unit

1.0 MHz

вҖ“ пҒӯs

вҖ“ пҒӯs

вҖ“ пҒӯs

вҖ“ пҒӯs

вҖ“ ns

вҖ“ ns

вҖ“ ns

300 ns

100 ns

вҖ“ пҒӯs

0.55 пҒӯs

вҖ“ пҒӯs

50 ns

Figure 14. Read Bus Timing Diagram

tR

` tF

tHIGH

tLOW

tSP

tSP

SCL

tSU:SDA

tBUF

SDA

1/fSCL

tHD:DAT

tSU:DAT

Start

Stop Start

tAA

tDH

Acknowledge

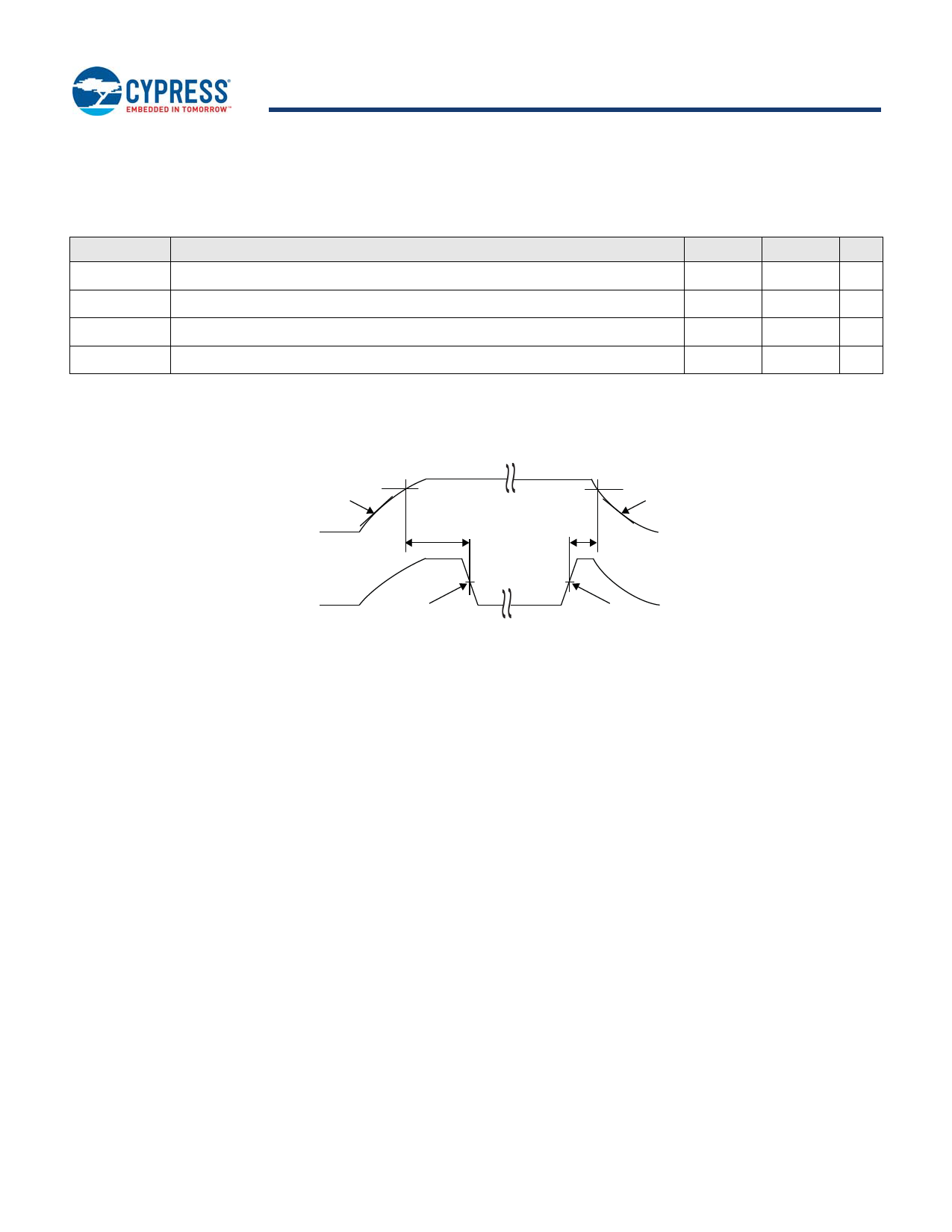

Figure 15. Write Bus Timing Diagram

SCL

SDA

tSU:STO

tHD:DAT

tHD:STA

tSU:DAT

tAA

Start

Stop Start

Acknowledge

Notes

5. Test conditions assume signal transition time of 10 ns or less, timing reference levels of VDD/2, input pulse levels of 0 to VDD(typ), and output loading of the specified

IOL and load capacitance shown in Figure 13.

6. The speed-related specifications are guaranteed characteristic points along a continuous curve of operation from DC to fSCL (max).

7. These parameters are guaranteed by design and are not tested.

Document Number: 001-84458 Rev. *D

Page 12 of 19