MFRC52201HN1/TRAYBM_10 データシートの表示(PDF) - NXP Semiconductors.

部品番号

コンポーネント説明

メーカー

MFRC52201HN1/TRAYBM_10 Datasheet PDF : 96 Pages

| |||

NXP Semiconductors

MFRC522

Contactless reader IC

8.1.4.4 Acknowledge

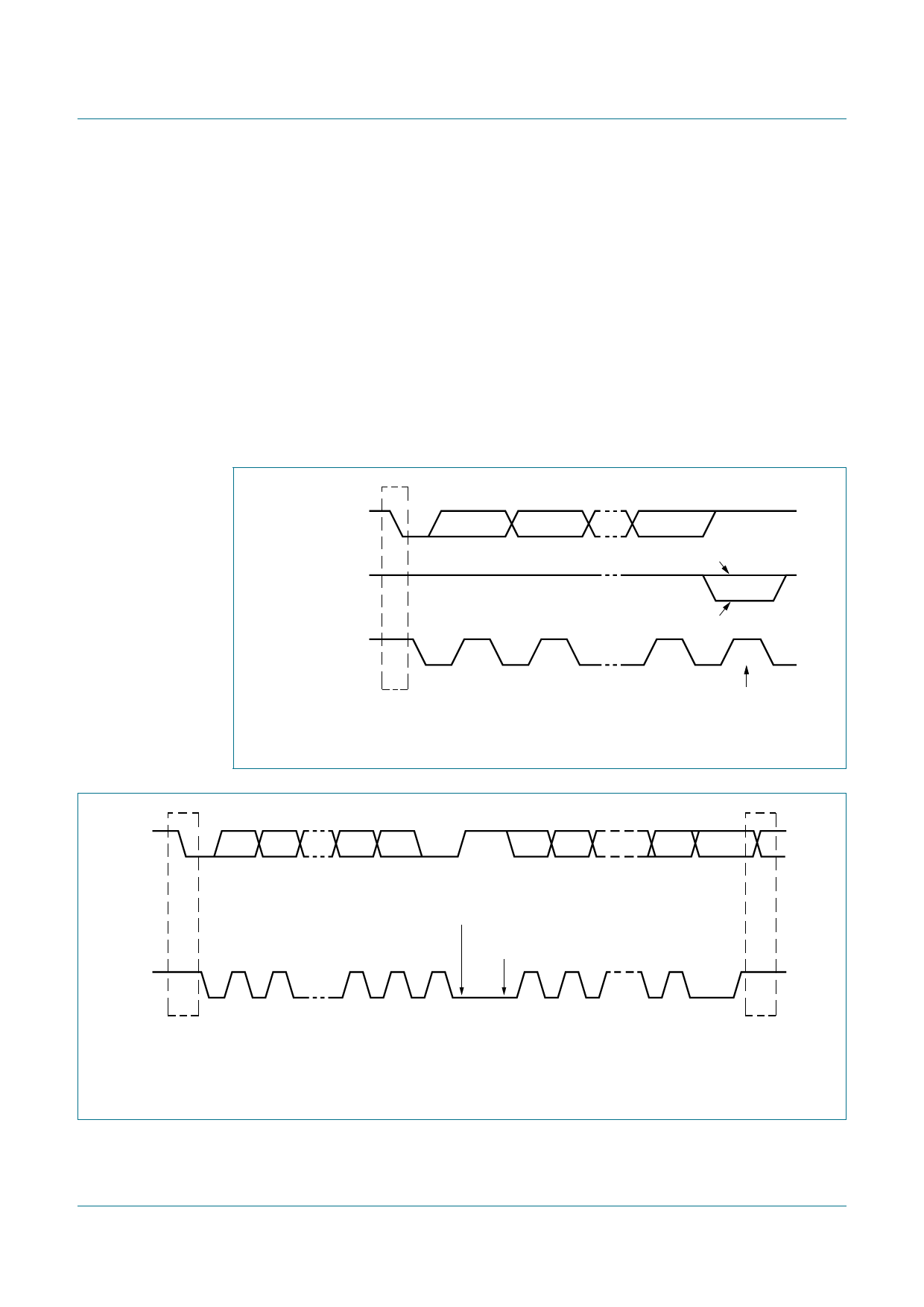

An acknowledge must be sent at the end of one data byte. The acknowledge-related clock

pulse is generated by the master. The transmitter of data, either master or slave, releases

the SDA line (HIGH) during the acknowledge clock pulse. The receiver pulls down the

SDA line during the acknowledge clock pulse so that it remains stable LOW during the

HIGH period of this clock pulse.

The master can then generate either a STOP (P) condition to stop the transfer or a

repeated START (Sr) condition to start a new transfer.

A master-receiver indicates the end of data to the slave-transmitter by not generating an

acknowledge on the last byte that was clocked out by the slave. The slave-transmitter

releases the data line to allow the master to generate a STOP (P) or repeated START (Sr)

condition.

data output

by transmitter

data output

by receiver

SCL from

master

S

1

2

START

condition

Fig 14. Acknowledge on the I2C-bus

not acknowledge

acknowledge

8

9

clock pulse for

acknowledgement

mbc602

SDA

MSB

SCL

S

or

1

2

7

Sr

START or

repeated START

condition

Fig 15. Data transfer on the I2C-bus

P

acknowledgement

signal from slave

byte complete,

interrupt within slave

clock line held LOW while

interrupts are serviced

acknowledgement Sr

signal from receiver

8

9

ACK

Sr

1

2

3-8

9

or

P

ACK

STOP or

repeated START

condition

msc608

MFRC522_34

Product data sheet

PUBLIC

All information provided in this document is subject to legal disclaimers.

Rev. 3.4 — 5 March 2010

112134

© NXP B.V. 2010. All rights reserved.

17 of 96