HMP8156 データシートの表示(PDF) - Intersil

部品番号

コンポーネント説明

メーカー

HMP8156 Datasheet PDF : 33 Pages

| |||

HMP8156

Following overlay processing, 2X upscaling may optionally

be applied to the pixel data. In this mode, the HMP8156

accepts SIF resolution video at 50 or 59.94 frames per sec-

ond and generates standard interlaced video at 262.5 lines

per field (240 active) at 59.94 fields per second for (M,

NSM) NTSC and (M) PAL, and 312.5 lines per field (288

active) at 50 fields per second for (B, D, G, H, I, N, CN) PAL.

This mode of operation allows SIF video to be upscaled to

full resolution and recorded on a VCR or displayed on a TV.

The input pixel data rate is reduced by half when 2X upscal-

ing is enabled. The color space conversion generates, and

the overlay mixer uses, 2:2:2 YCbCr data instead of 4:4:4

data. For rectangular pixel NTSC and PAL video, the input

rate is 6.75MHz during the active portion of each line instead

of 13.5MHz. Example SIF input resolutions and resulting

output resolutions are shown in Table 4.

frame of SIF size input has about the same number of lines

as a field of full size input. After 2X upscaling, the input is

4:4:4 YCbCr data ready for video processing.

Pixel Input and Control Signal Timing

The pixel input timing and the video control signal input/out-

put timing of the HMP8156 depend on the part’s operating

mode. The periods when the encoder samples its inputs and

generates its outputs are summarized in Table 5.

Figures 1-9 show the timing of CLK, CLK2, BLANK, and the

pixel and overlay input data with respect to each other.

BLANK may be an input or an output; the figures show both.

When it is an input, BLANK must arrive coincident with the

pixel and overlay input data; all are sampled at the same

time.

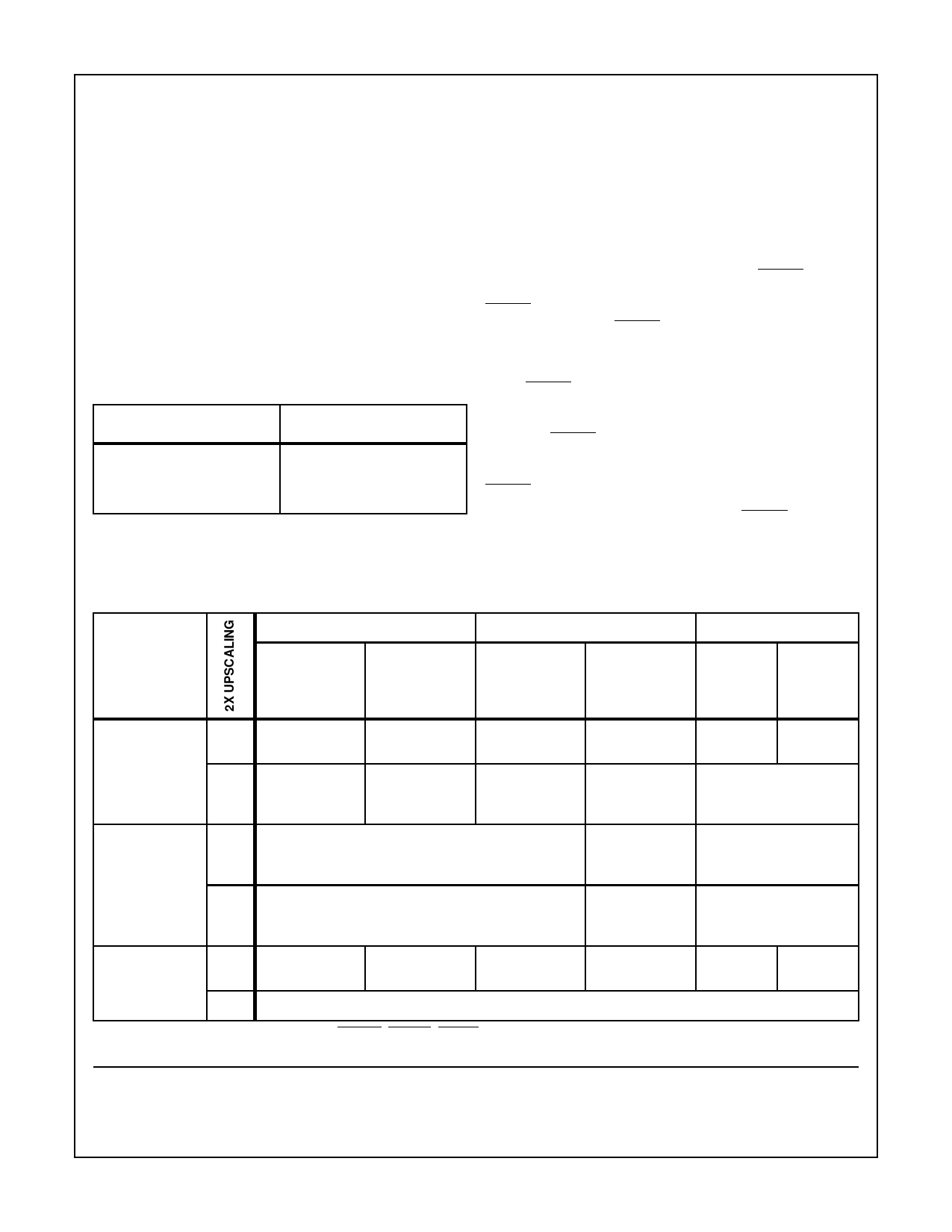

TABLE 4. TYPICAL RESOLUTIONS FOR 2X UPSCALING

When BLANK is an output, its timing with respect to the pixel

INPUT ACTIVE

RESOLUTION

352 x 240

352 x 288

320 x 240

384 x 288

OUTPUT ACTIVE

RESOLUTION

704 x 480

704 x 576

640 x 480

768 x 576

and overlay inputs depends on the blank timing select bit in

the timing_I/O_1 register. If the bit is cleared, the HMP8156

deasserts BLANK one CLK cycle before it samples the pixel

and overlay inputs. As shown in the timing figures, the

encoder samples the inputs 1-7 CLK2 periods after negating

BLANK, depending on the operating mode.

The HMP8156 performs horizontal 2X upscaling by linear

interpolation. The vertical scaling is done by line duplication.

For typical line duplication, the same frame of SIF pixel input

data is used for both the odd and even fields. Note that a

If the bit is set, the encoder deasserts BLANK during the

same CLK cycle in which it samples the input data. In effect,

the input data must arrive one CLK cycle earlier than when

the bit is cleared. This mode is not shown in the figures.

TABLE 5. PIXEL INPUT AND CONTROL SIGNAL I/O TIMING

INPUT PORT SAMPLING

VIDEO TIMING CONTROL (NOTE)

CLK FREQUENCY

INPUT FORMAT

PIXEL DATA OVERLAY DATA INPUT SAMPLE OUTPUT ON

INPUT

OUTPUT

8-Bit YCbCr

Off Every rising edge Same edge that Every rising edge Any rising edge of Ignored

of CLK2

latches Y

of CLK2

CLK2

One-half

CLK2

On Rising edge of Same edge that Rising edge of Rising edge of

CLK2 when CLK latches Y data CLK2 when CLK CLK2 when CLK

is low.

is low.

is high.

One-half CLK2

16-Bit YCbCr,

16-Bit RGB,

or

24-Bit RGB

Off Rising edge of CLK2 when CLK is low

On 2nd rising edge of CLK2 when CLK is low

Rising edge of

CLK2 when CLK

is high.

Either rising

CLK2 edge when

CLK is high

One-half CLK2

One-fourth CLK2

BT.656

Off Every rising edge Same edge that Not Allowed

of CLK2

latches Y

Any rising edge of Ignored

CLK2

One-half

CLK2

On

Not Available

NOTE: Video timing control signals include HSYNC, VSYNC, BLANK and FIELD. The sync and blanking I/O directions are independent;

FIELD is always an output.

8-Bit YCbCr Format without 2X Upscaling

enabled, the data is latched on each rising edge of CLK2.

When 8-bit YCbCr format is selected and 2X upscaling is not

The pixel data must be [Cb Y Cr Y’ Cb Y Cr Y’. . . ], with the

first active data each scan line being Cb data. Overlay data

5