MX469D3 データシートの表示(PDF) - MX-COM Inc

部品番号

コンポーネント説明

メーカー

MX469D3 Datasheet PDF : 17 Pages

| |||

1200/2400/4800bps MSK Modem

4

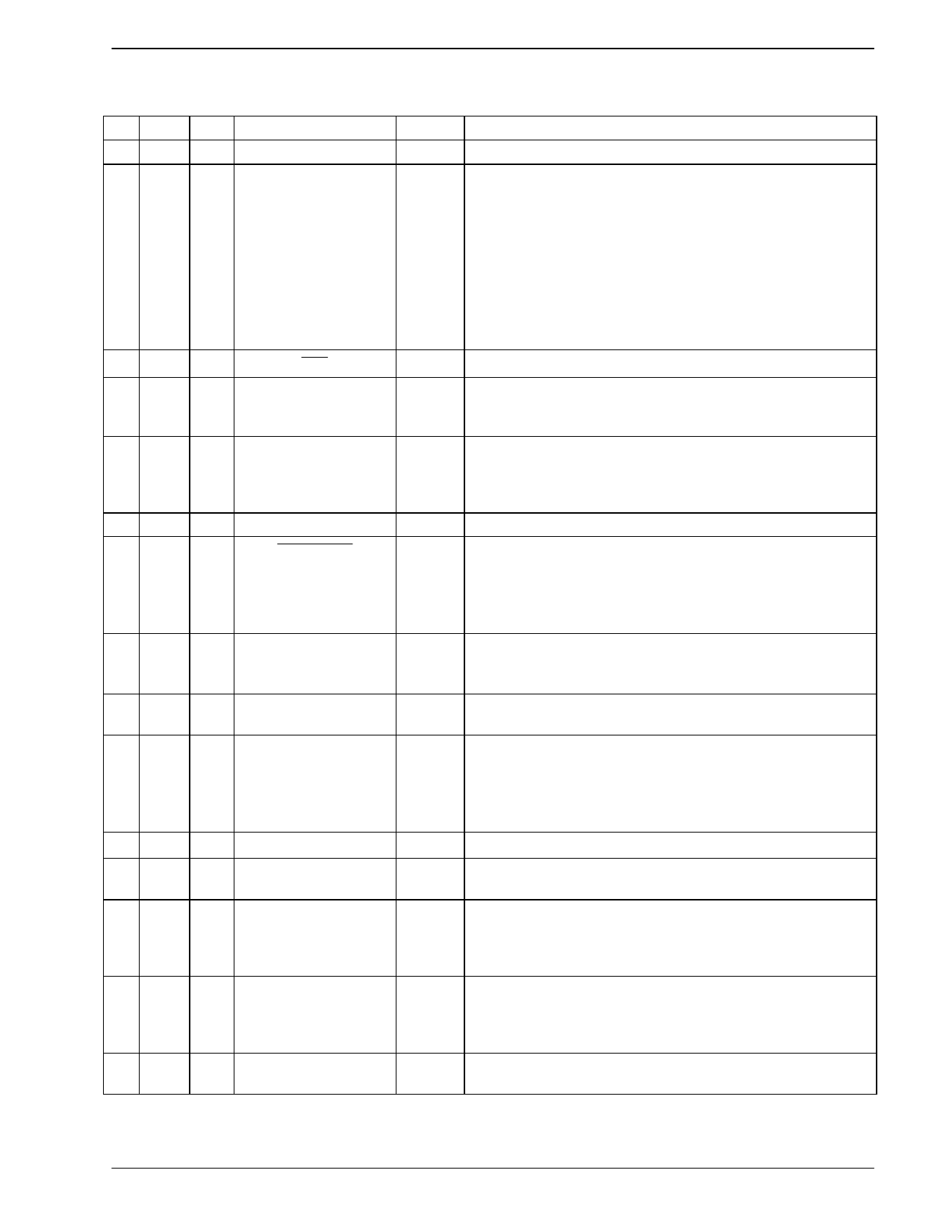

2. Signal List

MX469

P DW D3

11 1

22 2

33 3

55 4

67 5

78 6

89 7

9 10 8

10 11 9

11 12 10

12 13 11

13 14 12

14 15 13

15 16 14

Signal

Xtal/Clock

Xtal

TX Sync

TX Signal

TX Data

TX Enable

Bandpass

RX Enable

VBIAS

VSS

Unclocked Data

Clocked Data

Carrier Detect

RX Signal

Type Description

input

output

output

output

input

Input

output

Input

power

power

output

output

output

input

The input to the on-chip inverter, for use with either a

1.008MHz or a 4.032MHz Xtal or external clock. Clock

frequency selection is by the “Clock Rate” input pin. The

selection of this frequency will affect the operational Data

Rate of this device. Refer to Table 3. Operation of any

MX•COM IC without a Xtal or clock input may cause

device damage. To minimize damage in the event of a

Xtal/drive failure, it is recommended that a current

limiting device (resistor or fast-reaction fuse) be installed

on the power supply (VDD).

Output of the on-chip inverter.

A squarewave, produced on-chip, to synchronize the

input of logic data and transmission of the MSK signal

(See Figure 3).

When the transmitter is enabled, this pin outputs the

(140-step pseudo sinewave) MSK signal (See Figure 3).

With the transmitter disabled, this output is set to a high-

impedance state.

Serial logic data to be transmitted is input to this pin.

A logic ‘0’ will enable the transmitter (See Figure 3). A

logic ‘1’ at this input will put the transmitter into

powersave while forcing “TX Sync Out” to a logic ‘1’ and

“TX Signal Out” to a high-impedance state. This pin is

internally pulled to VDD.

The output of the RX Bandpass Filter. This output

impedance is typically 10k and may require buffering

prior to use.

The control of the RX function. The control of other

outputs is provided in Table 2

The output of the on-chip analog bias circuitry. Held

internally at VDD/2, this pin should be decoupled to VSS

by a capacitor (C2). See Figure 2 and RX Enable notes.

This bias voltage is maintained under all powersave

conditions.

Negative supply (GND).

The recovered asynchronous serial data output from the

receiver.

The recovered synchronous serial data output from the

receiver. Data is latched out by the recovered clock,

available at the “RX Sync O/P”. (See Figure 4 and

Figure 6).

For 1200 and 2400bps operation only. When an MSK

signal is being received this output is a logic ‘1’. The

Carrier Detect signal should be ignored during 4800bps

operation.

The MSK signal input for the receiver. This input should

be coupled via a capacitor, C3.

1998 MX-COM, Inc.

www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054

Doc. # 20480081.010

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA

All trademarks and service marks are held by their respective companies.