DM74LS244SJ データシートの表示(PDF) - Fairchild Semiconductor

部品番号

コンポーネント説明

メーカー

DM74LS244SJ Datasheet PDF : 6 Pages

| |||

August 1986

Revised March 2000

DM74LS244

Octal 3-STATE Buffer/Line Driver/Line Receiver

General Description

These buffers/line drivers are designed to improve both the

performance and PC board density of 3-STATE buffers/

drivers employed as memory-address drivers, clock driv-

ers, and bus-oriented transmitters/receivers. Featuring 400

mV of hysteresis at each low current PNP data line input,

they provide improved noise rejection and high fanout out-

puts and can be used to drive terminated lines down to

133Ω.

Features

s 3-STATE outputs drive bus lines directly

s PNP inputs reduce DC loading on bus lines

s Hysteresis at data inputs improves noise margins

s Typical IOL (sink current)

24 mA

s Typical IOH (source current) −15 mA

s Typical propagation delay times

Inverting

10.5 ns

Noninverting 12 ns

s Typical enable/disable time 18 ns

s Typical power dissipation (enabled)

Inverting

130 mW

Noninverting 135 mW

Ordering Code:

Order Number Package Number

Package Description

DM74LS244WM

M20B

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

DM74LS244SJ

M20D

20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

DM74LS244N

N20A

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

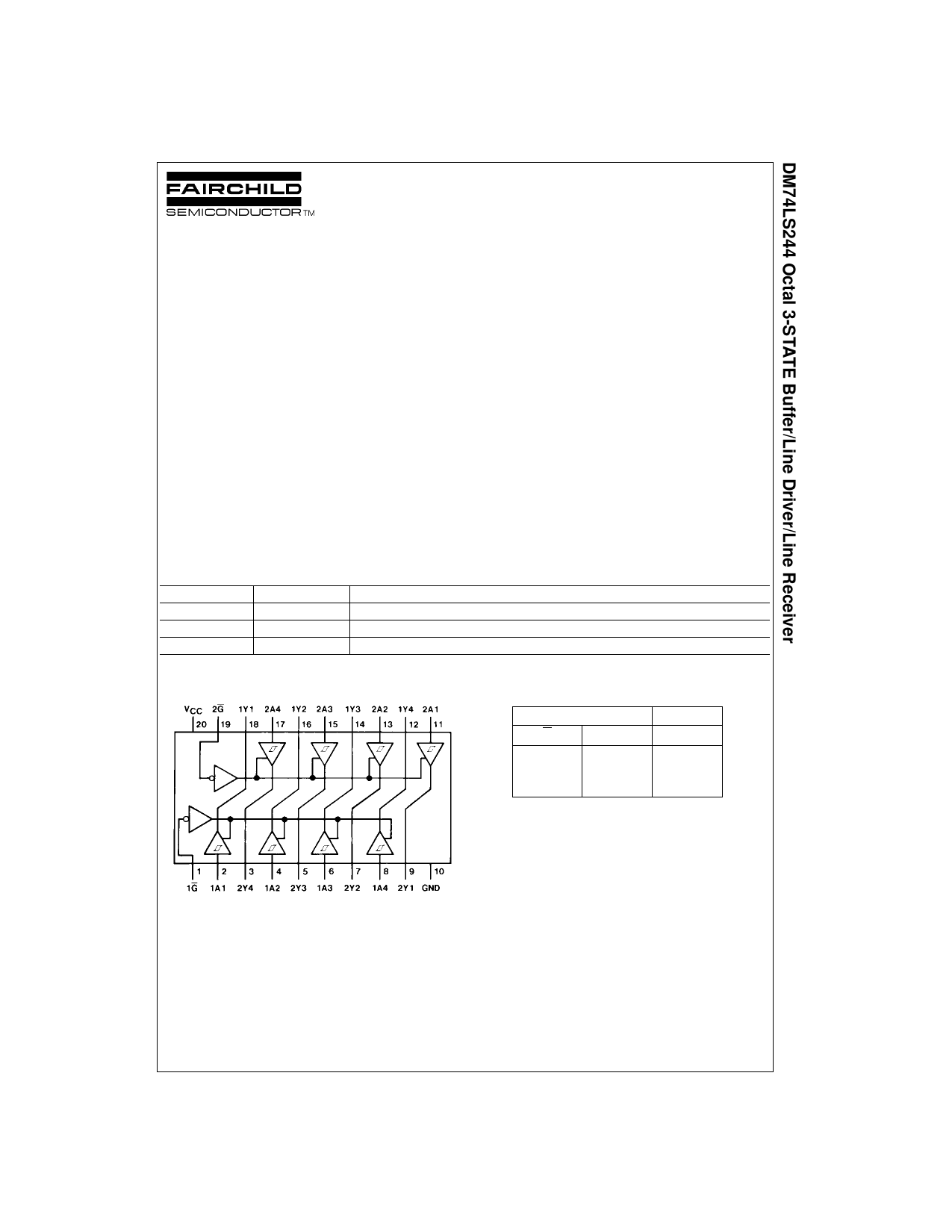

Connection Diagram

Function Table

Inputs

G

A

L

L

L

H

H

X

L = LOW Logic Level

H = HIGH Logic Level

X = Either LOW or HIGH Logic Level

Z = High Impedance

Output

Y

L

H

Z

© 2000 Fairchild Semiconductor Corporation DS008442

www.fairchildsemi.com