FS6312-71 データシートの表示(PDF) - AMI Semiconductor

部品番号

コンポーネント説明

メーカー

FS6312-71 Datasheet PDF : 6 Pages

| |||

AMERICAN MICROSYSTEMS, INC.

FS6312-71

Three-PLL Clock Generator IC

May 2000

Preliminary Information

1.0 Features

• Three PLLs with deep reference, feedback, and post

dividers to provide precision clock frequencies

• Multiple outputs provide several clocking options

• Outputs may be individually tristated for board testing

by the OE_x pins

• SUSPEND# pin completely powers down entire de-

vice

• Package: 16-pin, 5.3mm (0.209”) SSOP

• Custom frequency patterns, pinouts, and packages

are available. Contact your local AMI Sales Repre-

sentative for more information.

2.0 Description

The FS6312 is a ROM-based CMOS clock generator IC

designed to minimize cost and component count in a va-

riety of electronic systems.

Three low-jitter phase-locked loops (PLLs) drive up to five

clock outputs to provide a high degree of flexibility. The

device is packaged in a 16-pin SOIC to minimize board

space.

High-resolution divider capability permits generation of

desired frequencies.

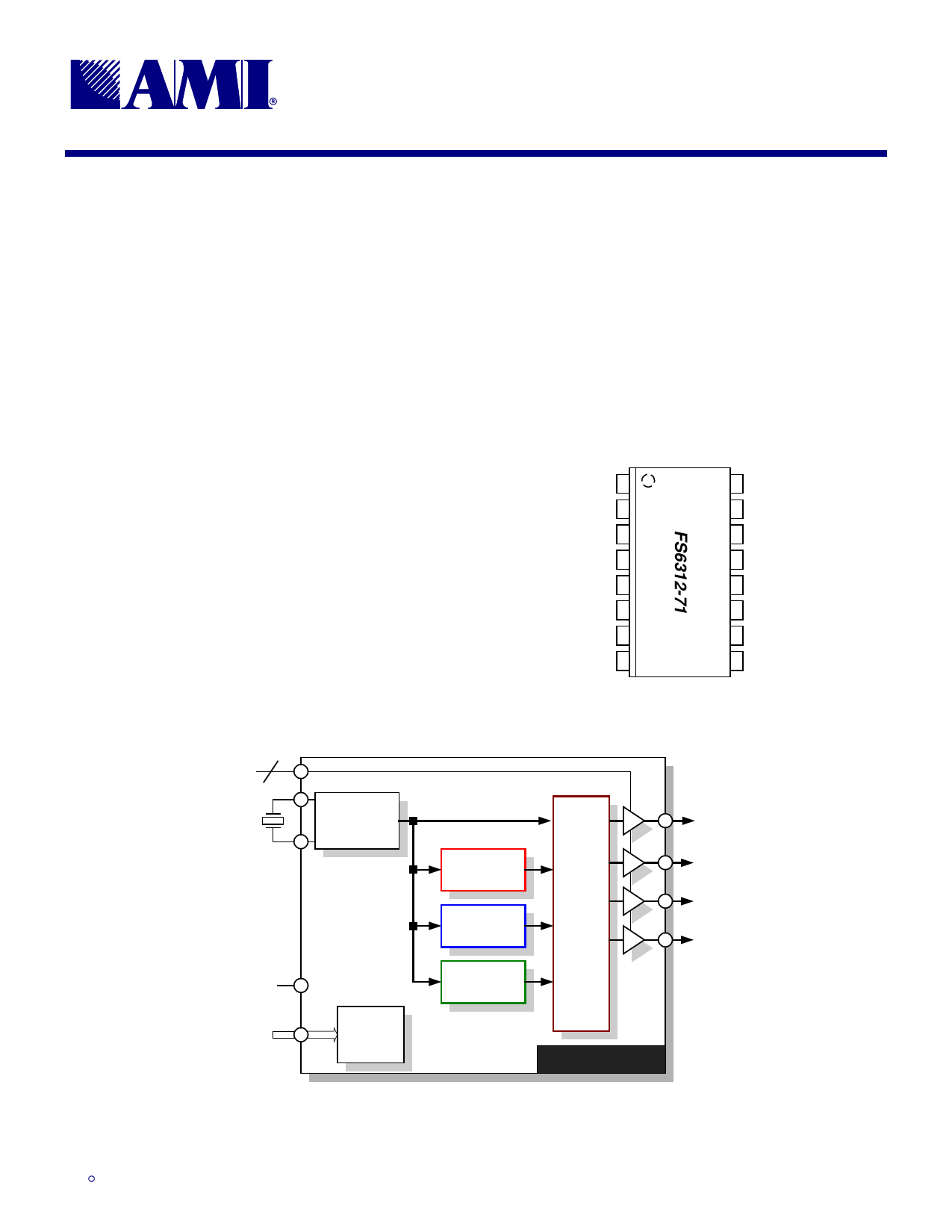

Figure 1: Pin Configuration

CLK_C 1

VDD 2

VSS 3

XIN 4

XOUT 5

OE_D 6

CLK_D 7

OE_B 8

16 OE_C

15 SUSPEND#

14 VDD

13 SELECT

12 OE_A

11 VSS

10 CLK_A

9 CLK_B

Figure 2: Block Diagram

OE x 4

XIN

XOUT

Crystal

Oscillator

SUSPEND#

SELECT

Device

Control

PLL A

PLL B

PLL C

Clock

Logic

CLK_A

CLK_B

CLK_C

CLK_D

FS6312-71

This document contains information on a preproduction product. American Microsystems, Inc. reserves the right to change or discontinue this product without notice.

ISO9001

5.23.00