IDT75K62134 データシートの表示(PDF) - Integrated Device Technology

部品番号

コンポーネント説明

メーカー

IDT75K62134 Datasheet PDF : 1 Pages

| |||

4.5M and 9M Network

Search Engine (NSE)

with LA-1 Interface

Product

Brief

IDT75K52134

IDT75K62134

To request the full datasheet, please contact your local

IDT Sales Representative or call 1-800-345-7015

Introduction

As part of the IDT IP Co-Processor product family, IDT delivers high

performance, feature-rich, easy-to-use, Network Search Engine (NSE)

products. Using CAM (Content Addressable Memory) technology, IDT

NSE products accelerate search functions for Access Control Lists (ACL),

Flow Caching, and forwarding to improve performance in next generation

networking equipment.

Device Description

The NSE with a single LA-1 interface is intended to work with any NPU

having a LA-1 look aside interface. Multiple devices including the LA-1

NSE can be connected to the same LA-1 interface. Each LA-1 NSE device

may be point-to-point expanded up to eight NSE devices.

NSE Features

◆ 128K x 72 (9M) or 64K x 72 (4.5M) Data and Mask cells

◆ Full Ternary Content Addressable Memory

◆ Advanced Database Management

- SelectableDatabases

- ProgrammableWidthperDatabase

- Lookup widths from 32 to 576 bits

- Only the selected Database is powered

◆ LookupInstructions

- Standard Lookup

- Multi-HitLookup

- Multi-DatabaseLookup

- Re-Issue Multi-Database Lookup

◆ Maintenance Features

- Aging

- MultiHitInvalidate

- Learn per Database

◆ Multi-Context support

◆ Pool of (72-bit) Global Mask Registers (shared across contexts)

◆ In-Band Control and Management

◆ Assoicated Data SRAM is supported through a glue-less ZBT®

interface

◆ Lowest Power per Application

◆ Synchronous Pipeline Operation

◆ Boundary Scan JTAG Interface

◆ 1.2V Core Supply

◆ 1.5V HSTL I/O Supply

◆ 2.5V I/O Supply for ZBT® Associated Data SRAM

◆ 35mm x 35mm BGA Package

External Interfaces

The following external interfaces are supported by the LA-1 NSE device

◆ Single LA-1 NPU interface

- LA-1 Clock Frequency up to 250 MHz

- Supports LA-1 burst of 2

- Echo clocks supported (CQ, CQ)

◆ Point-to-PointCascadingInterface

- Up to eight NSEs can be cascaded using this scheme

◆ Associated Data SRAM with standard ZBT® Interface

◆ Boundary Scan JTAG Interface (IEEE 1149.1)

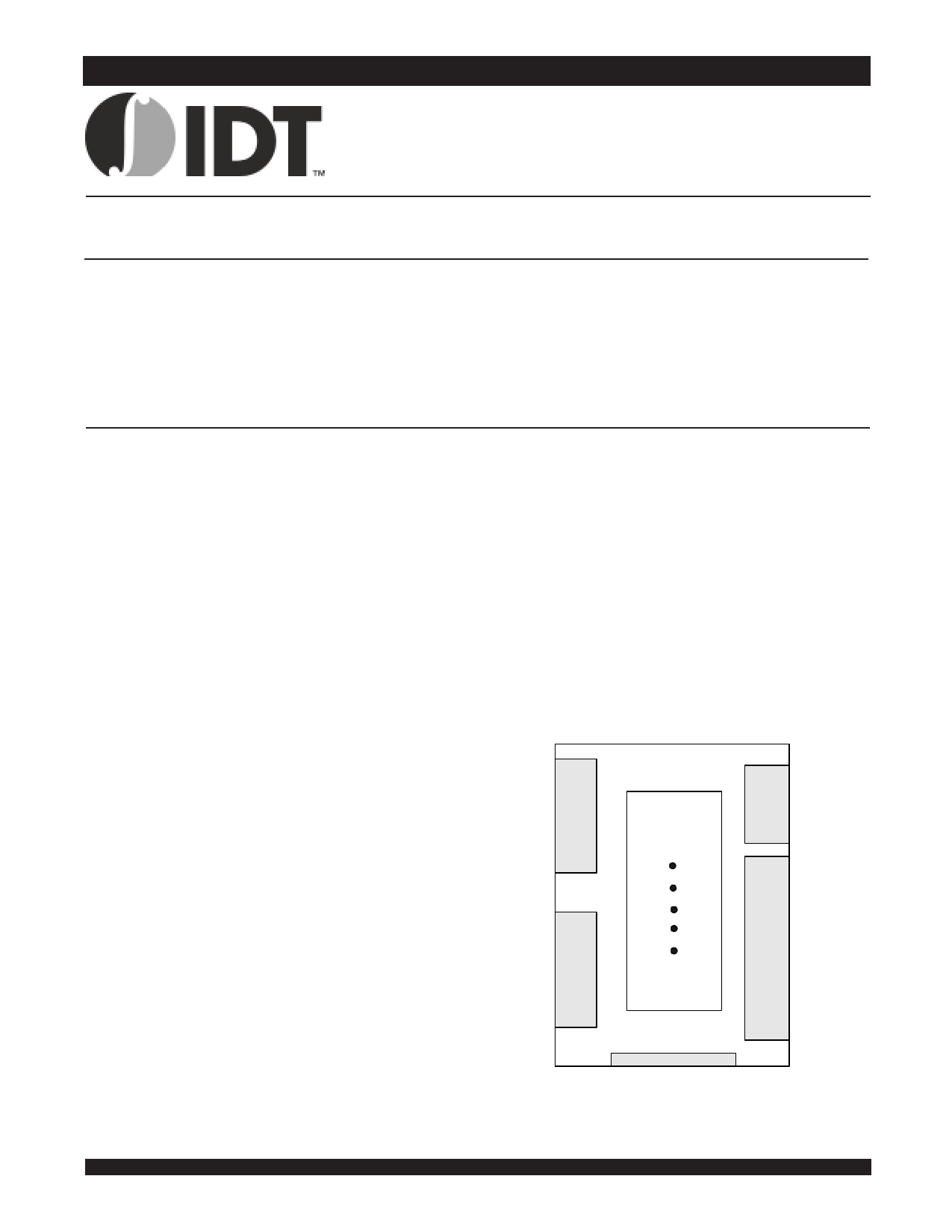

Figure 1.0 LA-1 NSE External Interfaces

QDR

Read

Control

Logic

256K x 36 Full

Ternary Content

Addressable Memory

Cascade

Interface

QDR

Write

Control

Logic

ZBT

Interface

JTAG Interface

6070 drw04aa

JANUARY 2003

1

2002 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice.

DSC-6070/00

ZBT and ZeroBus Turnaround are trademarks of Integrated Device Technology, Inc. and the architecture is supported by Micron Technology and Motorola Inc.

QDR™ - Quad Data Rate (Trademark of Cypress, IDT, Micron, NEC and Samsung.) All brands or products are the trademarks or registered trademarks of their

respective owners.