MAX6880 データシートの表示(PDF) - Maxim Integrated

部品番号

コンポーネント説明

メーカー

MAX6880 Datasheet PDF : 19 Pages

| |||

Dual-/Triple-Voltage, Power-Supply

Sequencers/Supervisors

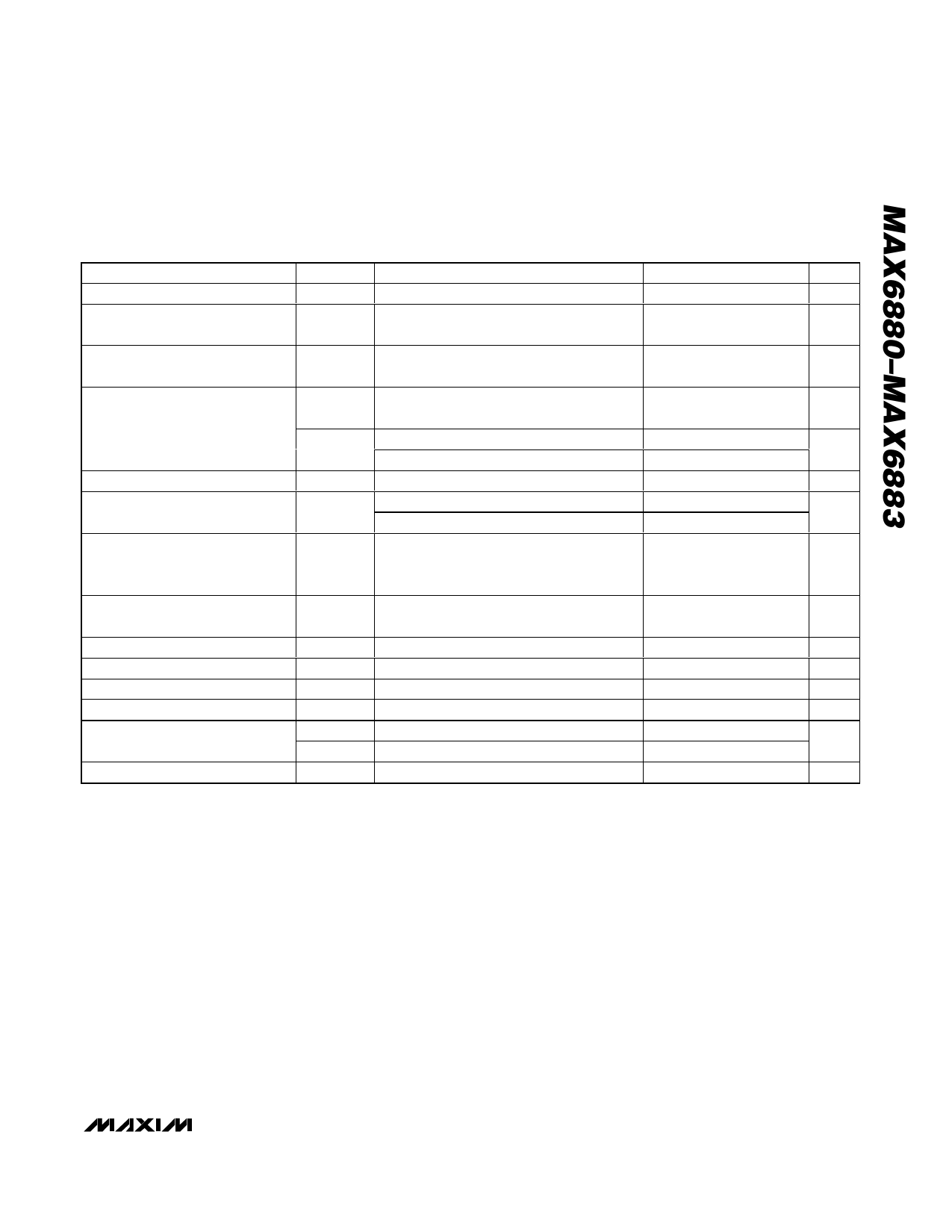

ELECTRICAL CHARACTERISTICS (continued)

(IN1, IN2, or IN3 = +2.7V to +5.5V, EN/UV = MARGIN = ABP, TA = -40°C to +85°C, unless otherwise specified. Typical values are

at TA = +25°C, unless otherwise noted.) (Note 1)

Power-Good Threshold

Power-Good Threshold Hysteresis

GATE_ Output High

VTH_PG VOUT_ falling

VHYS_PG VOUT_ rising

VGOH ISOURCE = 0.5µA

91.5 92.5 93.5

%

0.5

%

IN_ + IN_ + IN_ +

V

4.2

5.0

5.8

GATE_ Pullup Current

IGUP

During power-up and power-down,

VGATE_ = 1V

2.5

4

µA

GATE_ Pulldown Current

SET_ to GATE_ Delay

PG/RST Output Low

IGD

During power-up and power-down,

VGATE_ = 5V

2.5

4

µA

IGDS

When disabled, VGATE_ = 5V, VIN_ ≥ 2.7V

When disabled, VGATE_ = 5V, VIN_ ≥ 4V

9.5

mA

20

tD-GATE SET falling, 25mV overdrive

10

µs

VOL

VIN_ ≥ 2.7V, ISINK = 1mA, output asserted

VIN_ ≥ 4.0V, ISINK = 4mA, output asserted

0.3

V

0.4

Differential between each of the OUT_ and

Tracking Differential Voltage Stop

Ramp

VTRK

the ramp voltage during power-up and

power-down, Figure 1 (Note 5)

75

125

180

mV

Tracking Differential Fault Voltage

VTRK_F

Differential between each of the OUT_ and

the ramp voltage, Figure 1 (Note 5)

200

250

310

mV

Power-Low Threshold

Power-Low Hysteresis

OUT to GND Pulldown Impedance

MARGIN Pullup Current

MARGIN Input Voltage

MARGIN Glitch Rejection

VTH_PL OUT_ falling

VTH_PLHYS OUT_ rising

IN_ > 2.7V (Note 6)

IIN

VIL

VIH

125

142

170

mV

10

mV

100

Ω

7

10

13

µA

0.8

V

2.0

100

ns

Note 1: Specifications guaranteed for the stated global conditions. 100% production tested at TA = +25°C and TA = +85°C.

Specifications at TA = -40°C to +85°C are guaranteed by design. These devices meet the parameters specified when at

least one of IN1/IN2/IN3 is between 2.7V to 5.5V, while the remaining IN1/IN2/IN3 are between 0 and 5.5V.

Note 2: A current ID = 2.5µA ±15% is generated internally and is used to set the DELAY and TIMEOUT periods and used as a refer-

ence for tDELAY and tTIMEOUT.

Note 3: The total DELAY is tDELAY = 200µs + (500kΩ x CDELAY). Leave DELAY unconnected for 200µs delay. The total TIMEOUT is

tTIMEOUT = 200µs + (500kΩ x CTIMEOUT). Leave TIMEOUT unconnected for 200µs timeout.

Note 4: A current IS = 25µA ±10% is generated internally and used as a reference for tFAULT, tRETRY, and slew rate.

Note 5: During power-up, only the condition OUT_ < ramp - VTRK is checked in order to stop the ramp. However, both conditions

OUT_ < ramp – VTRK_F and OUT_ > ramp + VTRK_F cause a fault. During power-down, only the condition OUT > ramp +

VTRK is checked in order to stop the ramp. However, both conditions OUT_ < ramp - VTRK_F and OUT_ > ramp + VTRK_F

cause a fault (see Figure 10). Therefore, if OUT1, OUT2, and OUT3 (during power-up tracking and power-down) differ by

more than 2 x VTRK_F, a fault condition is asserted.

Note 6: A 100Ω pulldown to GND activated by a fault condition. See the Internal Pulldown section.

_______________________________________________________________________________________ 3