MAX6880 データシートの表示(PDF) - Maxim Integrated

部品番号

コンポーネント説明

メーカー

MAX6880 Datasheet PDF : 19 Pages

| |||

Dual-/Triple-Voltage, Power-Supply

Sequencers/Supervisors

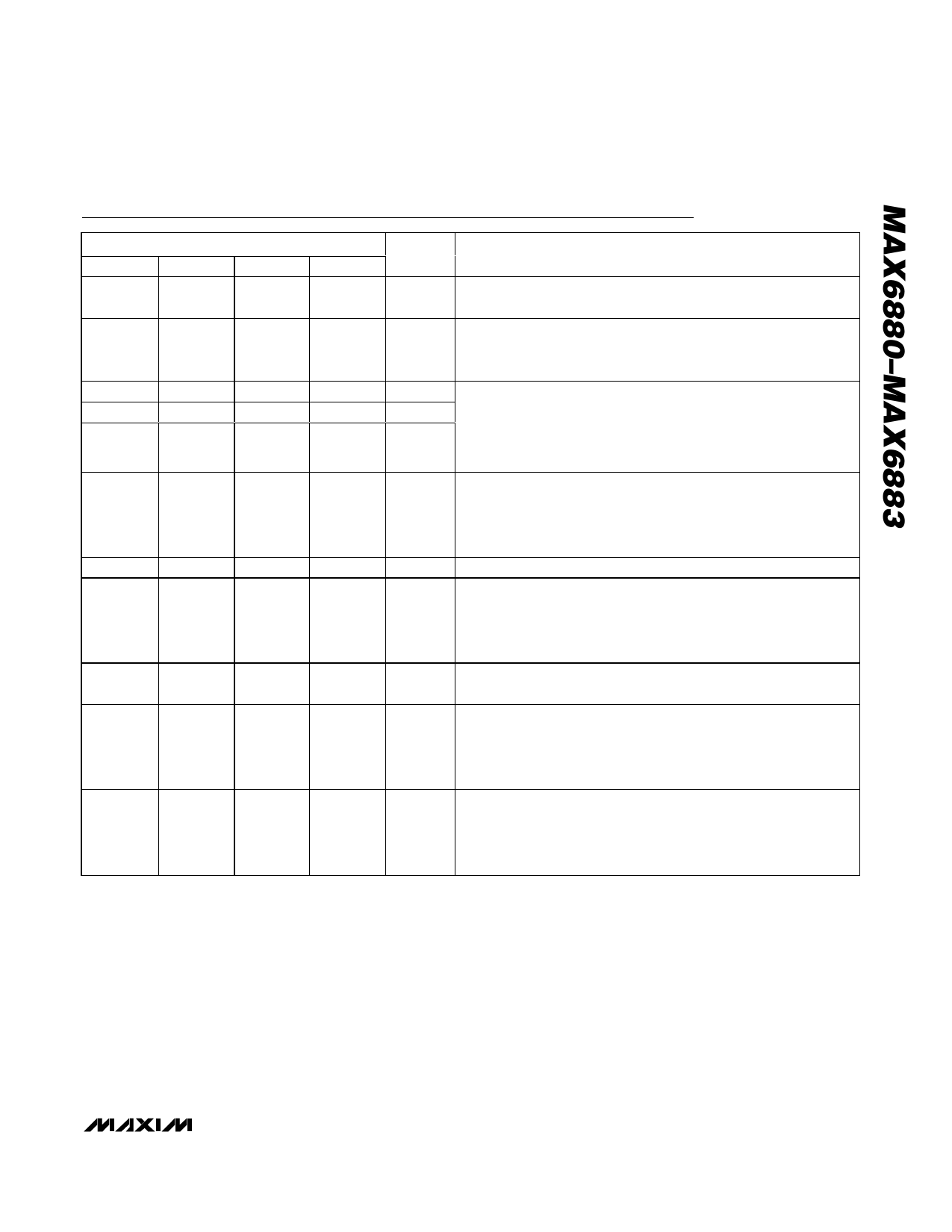

Pin Description

MAX6880

1, 11,

12, 15

PIN

MAX6881 MAX6882

—

—

MAX6883

1, 8, 9, 10

NAME

FUNCTION

N.C. No Connection. Not internally connected.

Internal Supply Bypass Input. Bypass ABP with a 1µF capacitor to

2

—

1

—

ABP GND. ABP maintains the device supply voltage during rapid power-

down conditions.

3

2

—

—

SET3 Externally Adjusted IN_ Undervoltage Lockout Threshold. Connect

4

3

2

2

SET2 SET_ to an external resistor-divider network to set the desired

undervoltage threshold for each IN_ supply (see the Typical

5

4

3

3

SET1 Application Circuit). All SET_ inputs must be above the internal

SET_ threshold (0.5V) to enable sequencing functionality.

Logic-Enable Input or Undervoltage Lockout Monitor Input. EN/UV

must be high (EN/UV > VEN_R) to enable voltage sequencing

6

5

4

4

EN/UV power-up operation. OUT_ begins tracking down when EN/UV <

VEN_F. Connect EN/UV to an external resistor-divider network to set

the external UVLO threshold.

7

6

5

5

GND Ground

Sequence Delay Select Input. Connect a capacitor from DELAY

to GND to select the desired delay period before sequencing is

8

7

6

6

DELAY enabled (after all SET_ inputs and EN/UV are above their respective

thresholds) or between supply sequences. Leave DELAY

unconnected for the default 200µs delay period.

9

8

7

7

SLEW Slew-Rate Adjustment Input. Connect a capacitor from SLEW

to GND to select the desired OUT_ slew rate.

PG/RST Timeout Period Adjust Input. PG/RST asserts high after the

timeout period when all OUT_ exceed their IN_ referenced

10

—

8

—

TIMEOUT threshold. Connect a capacitor from TIMEOUT to GND to set the

desired timeout period. Leave TIMEOUT unconnected for the

default 200µs delay period.

Margin Input, Active-Low. Drive MARGIN low to enable margin

mode (see the Margin section). The MARGIN functionality is

13

—

9

—

MARGIN disabled (returns to normal monitoring mode) after MARGIN returns

high. MARGIN is internally pulled up to ABP through a 10µA

current source.

_______________________________________________________________________________________ 9