MC-4532DA726PFB-A10 データシートの表示(PDF) - NEC => Renesas Technology

部品番号

コンポーネント説明

メーカー

MC-4532DA726PFB-A10

MC-4532DA726PFB-A10 Datasheet PDF : 16 Pages

| |||

DATA SHEET

MOS INTEGRATED CIRCUIT

MC-4532DA726

32 M-WORD BY 72-BIT SYNCHRONOUS DYNAMIC RAM MODULE

REGISTERED TYPE

Description

The MC-4532DA726 is a 33,554,432 words by 72 bits synchronous dynamic RAM module on which 18 pieces of

128M SDRAM: µPD45128441 are assembled.

These modules provide high density and large quantities of memory in a small space without utilizing the surface-

mounting technology on the printed circuit board.

Decoupling capacitors are mounted on power supply line for noise reduction.

Features

• 33,554,432 words by 72 bits organization (ECC type)

• Clock frequency and access time from CLK

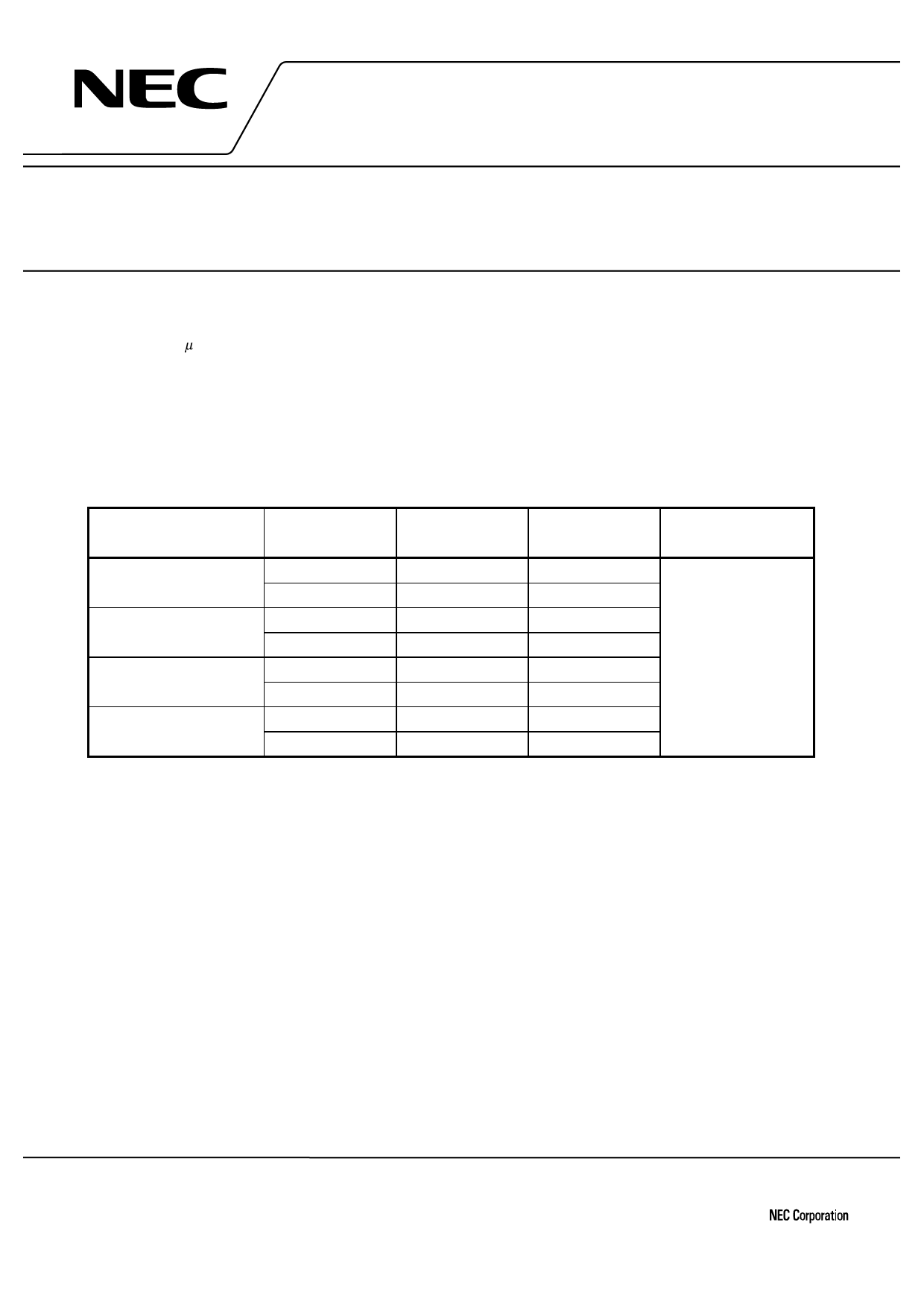

Part number

/CAS latency

Clock frequency

(MAX.)

Access time from CLK

(MAX.)

Module type

MC-4532DA726EFB-A80

CL = 3

125 MHz

6 ns

PC100 Registered DIMM

CL = 2

100 MHz

6 ns

Rev. 1.2 Compliant

MC-4532DA726EFB-A10

CL = 3

100 MHz

6 ns

CL = 2

77 MHz

7 ns

5 MC-4532DA726PFB-A80

CL = 3

125 MHz

6 ns

CL = 2

100 MHz

6 ns

5 MC-4532DA726PFB-A10

CL = 3

100 MHz

6 ns

CL = 2

77 MHz

7 ns

• Fully Synchronous Dynamic RAM, with all signals referenced to a positive clock edge

• Pulsed interface

• Possible to assert random column address in every cycle

• Quad internal banks controlled by BA0 and BA1 (Bank Select)

• Programmable burst-length (1, 2, 4, 8 and Full Page)

• Programmable wrap sequence (Sequential / Interleave)

• Programmable /CAS latency (2, 3)

• Automatic precharge and controlled precharge

• CBR (Auto) refresh and self refresh

• All DQs have 10 Ω ± 10 % of series resistor

• Single 3.3 V ± 0.3 V power supply

• LVTTL compatible

• 4,096 refresh cycles / 64 ms

• Burst termination by Burst Stop command and Precharge command

• 168-pin dual in-line memory module (Pin pitch = 1.27 mm)

• Registered type

• Serial PD

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. M13633EJ7V0DS00 (7th edition)

The mark 5 shows major revised points.

Date Published February 2000 NS CP(K)

Printed in Japan

©

1998