SPT574B „Éá„Éľ„āŅ„ā∑„Éľ„Éą„ĀģŤ°®Á§ļÔľąPDFÔľČ - Cadeka Microcircuits LLC.

ťÉ®ŚďĀÁē™ŚŹ∑

„ā≥„É≥„ÉĚ„Éľ„Éć„É≥„ÉąŤ™¨śėé

„É°„Éľ„āę„Éľ

SPT574B Datasheet PDF : 12 Pages

| |||

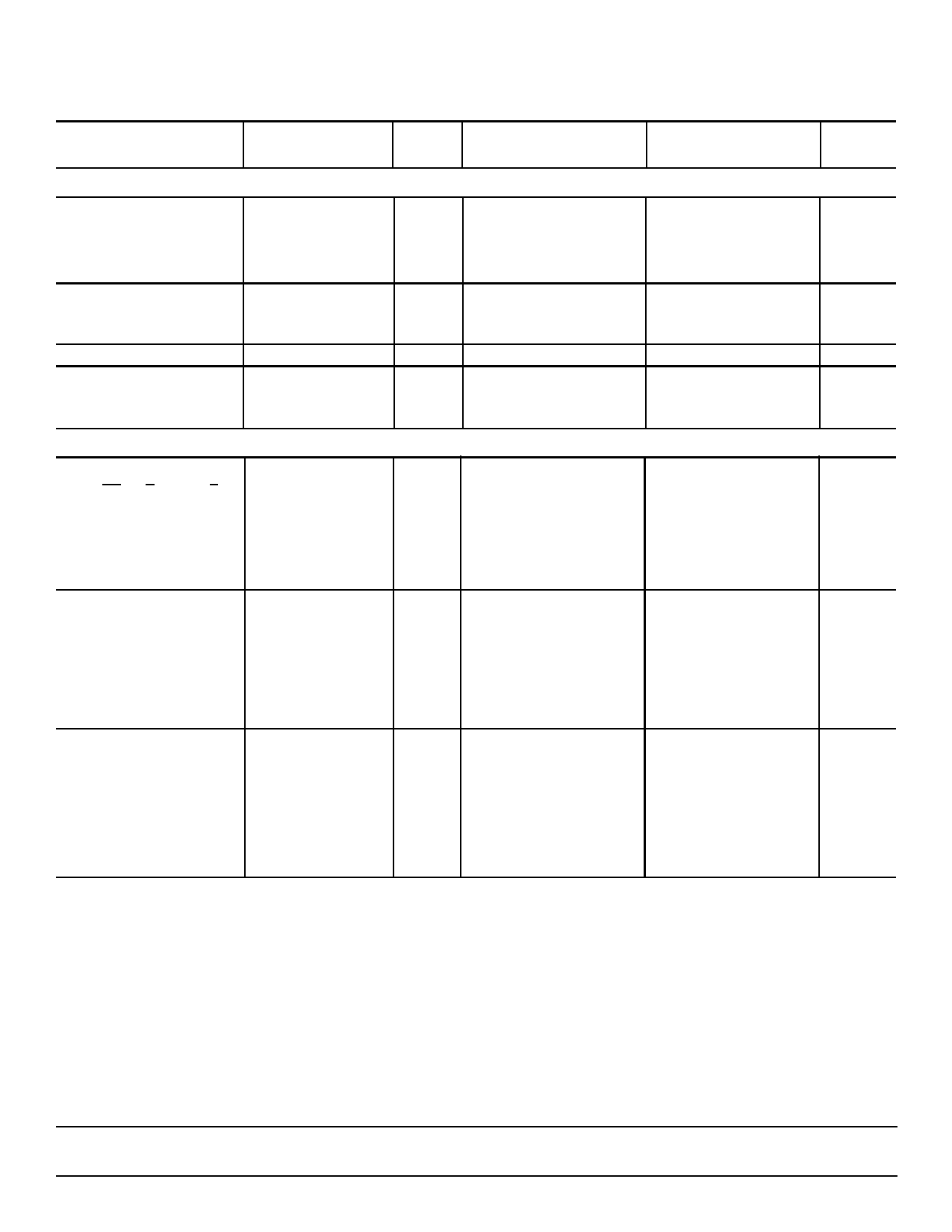

ELECTRICAL SPECIFICATIONS

TA = TMIN to TMAX, VEE = 0 to +5 V, VDD = +5 V, fS = 40 kHz, fIN = 10 kHz, unless otherwise specified.

PARAMETER

TEST

CONDITIONS

DC ELECTRICAL CHARACTERISTICS

TEST

LEVEL

SPT574C

MIN TYP MAX

SPT574B

MIN TYP MAX UNITS

Power Supplies Operating

Voltage Range

VDD

VEE2

Operating Current

IDD

IEE2

Power Dissipation

Internal Reference

Voltage

Output Current3

VEE = +5 V

IV

+4.5

IV

+5.5

VDD

+4.5

+5.5 Volts

VDD Volts

IV

13

20

13

20 mA

IV

167

167

¬ĶA

VI

65 100

65 100 mW

VI

2.4

2.5

2.6

2.4

2.5

2.6 Volts

VI

0.5

0.5

mA

DIGITAL CHARACTERISTICS

Logic Inputs

(CE, CS , R/C , Ao, 12/8 )

Logic 0

Logic1

VI

-0.5

VI

2.0

+0.8 -0.5

5.5

2.0

+0.8 Volts

5.5 Volts

Current

VI

-5.0 0. 1

5.0 -5.0 0. 1

5.0 ¬ĶA

Capacitance

Logic Outputs

(DB11-DB0, STS)

Logic 0

Logic 1

Leakage

Capacitance

V

(ISink = 1.6 mA)

VI

(ISOURCE = 500 ¬ĶA)

VI

(High Z State,

VI

DB11-DB0 Only)

V

5

5

pF

+2.4

-5

+0.4

+2.4

0.1

+5

-5

5

+0.4 Volts

Volts

0.1

+5 ¬ĶA

5

pF

AC Accuracy

fS=40 kHz, fIN=10 kHz

Spurious Free Dyn. Range

V

78

78

dB

Total Harmonic Distortion

V

-77

-77

dB

Signal-to-Noise Ratio

V

72

72

dB

Signal-to-Noise & Distortion

V

71

71

dB

(SINAD)

Intermodulation Distortion fIN=10 kHz;

V

-75

fIN2=11.5 kHz

Note 1: Fixed 50 ‚Ą¶ resistor from REF OUT to REF IN and REF OUT to BIP OFF.

-75

dB

Note 2: VEE is optional and is only used to set the mode for the internal sample/hold. When not using VEE, the pin should be treated

as a no connect. If VEE is connected to 0 to -15 V, aperture delay (tAP) will increase from 20 ns (typ) to 4000 ns (typ).

Note 3: Available for external loads; external load should not change during conversion.

SPT574

3

8/1/00