ST16C550(2003) データシートの表示(PDF) - Exar Corporation

部品番号

コンポーネント説明

メーカー

ST16C550 Datasheet PDF : 35 Pages

| |||

ST16C550

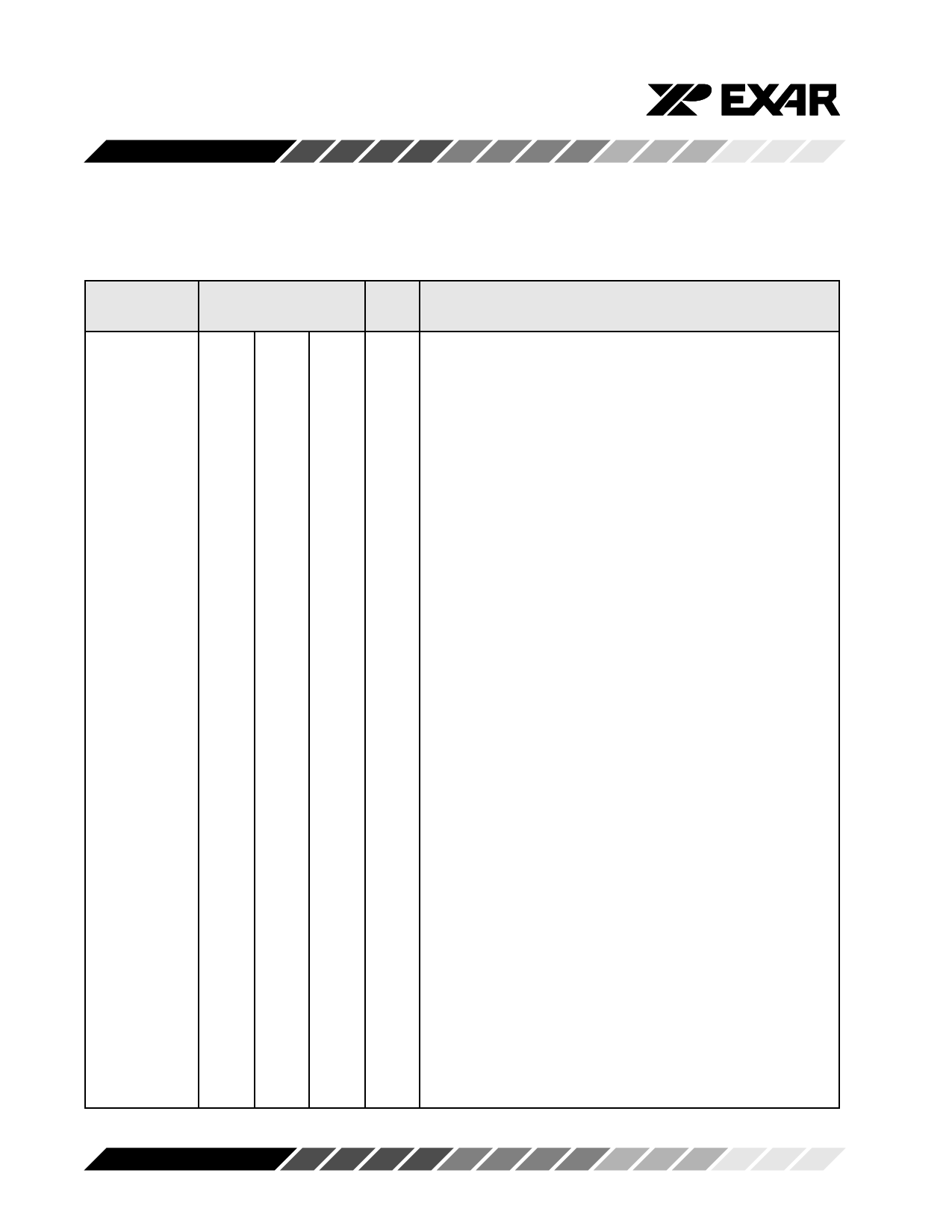

SYMBOL DESCRIPTION

Symbol

A0

A1

A2

IOR

CS0

CS1

-CS2

IOW

-AS

D0-D7

GND

Pin

Signal

40 44 48 type

Pin Description

28 31 28

I Address-0 Select Bit Internal registers address selection.

27 30 27

I Address-1 Select Bit Internal registers address selection.

26 29 26

I Address-2 Select Bit Internal registers address selection.

22 25 20

I Read data strobe. Its function is the same as -IOR (see -

IOR), except it is active high. Either an active -IOR or IOR

is required to transfer data from 16C550 to CPU during a

read operation. Connect to logic 0 when using -IOR.

12 14

9

I Chip Select-0. Logical 1 on this pin provides the chip select-

0 function. Connect CS0 to logic 1 if using CS1 or -CS2.

13 15 10

I Chip Select-1. Logical 1 on this pin provides the chip select-

1 function. Connect CS1 to logic 1 if using CS0 or -CS2.

14 16 11

I Chip Select -2. Logical 0 on this pin provides the chip select-

2 function. Connect to logic 0 if using CS0 or CS1.

19 21 17

I Write data strobe. Its function is the same as -IOW (see -

IOW), but it acts as an active high input signal. Either -IOW

or IOW is required to transfer data from the CPU to

ST16C550 during a write operation. Connect to logic 0 when

using -IOW.

25 28 24

I Address Strobe. A logic 1 transition on -AS latches the state

of the chip selects and the register select bits, A0-A2. This

input is used when address and chip selects are not stable

for the duration of a read or write operation, i.e., a micropro-

cessor that needs to de-multiplex the address and data bits.

If not required, the -AS input can be permanently tied to a

logic 0.

1-8 2-9 43-47

2-4 I/O Data Bus (Bi-directional) - These pins are the eight bit, tri-

state data bus for transferring information to or from the

controlling CPU. D0 is the least significant bit and the first

data bit in a transmit or receive serial data stream.

20 22 18 Pwr Signal and Power Ground.

Rev. 4.30

4