AT90S4414 データシートの表示(PDF) - Atmel Corporation

部品番号

コンポーネント説明

メーカー

AT90S4414 Datasheet PDF : 10 Pages

| |||

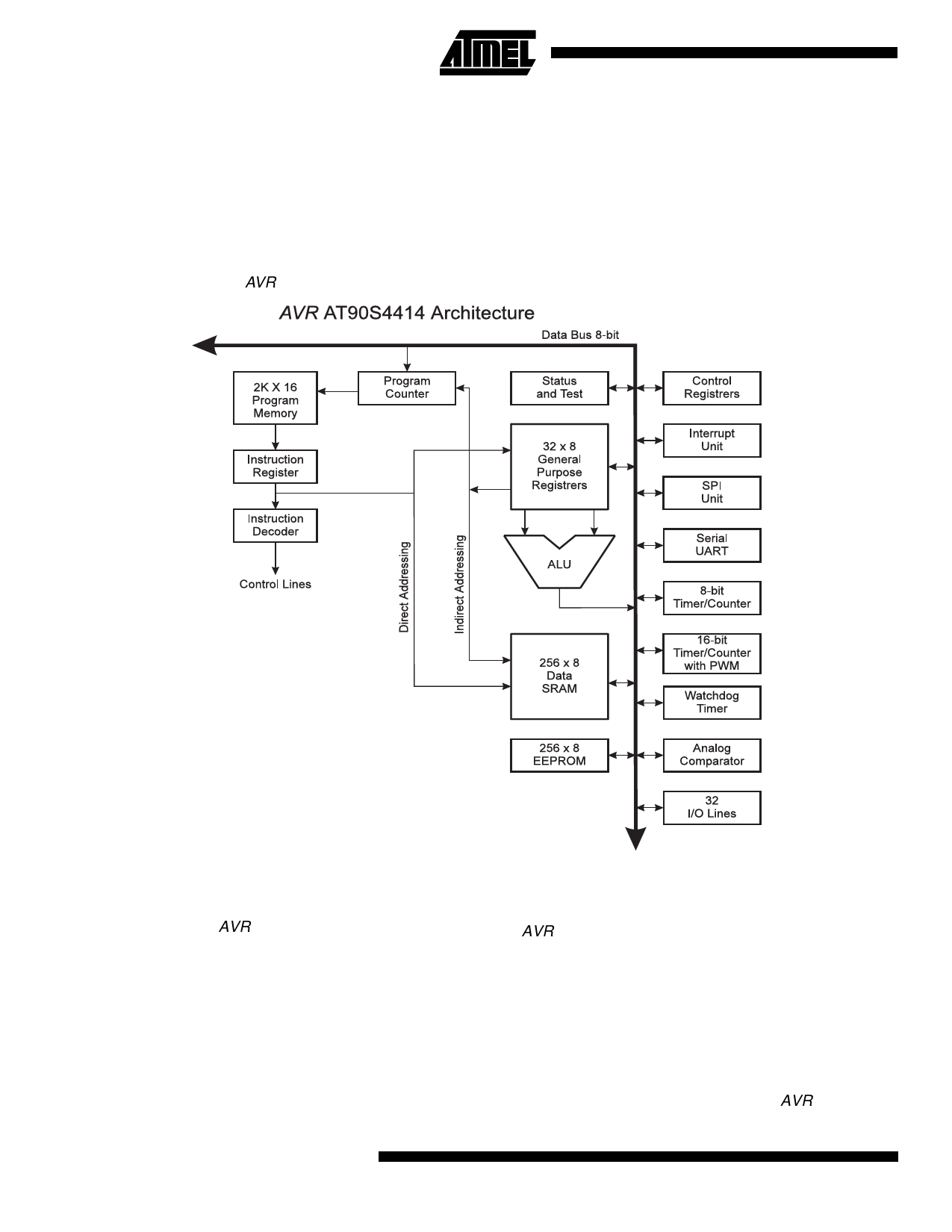

AT90S4414 Architectural Overview

The fast-access register file concept contains 32 x 8-bit

general purpose working registers with a single clock cycle

access time. This means that during one single clock cycle,

one ALU (Arithmetic Logic Unit) operation is executed. Two

operands are output from the register file, the operation is

executed, and the result is stored back in the register file -

in one clock cycle. Six of the 32 registers can be used as

three 16-bits indirect address register pointers for Data

Space addressing - enabling efficient address calculations.

One of the three address pointers is also used as the

address pointer for the constant table look up function.

These added function registers are the 16-bits X-register,

Y-register and Z-register.

Figure 4. The AT90S4414 AVR Enhanced RISC Architecture

The ALU supports arithmetic and logic functions between

registers or between a constant and a register. Single reg-

ister operations are also executed in the ALU. Figure 4

shows the AT90S4414 AVR Enhanced RISC microcontrol-

ler architecture.

In addition to the register operation, the conventional mem-

ory addressing modes can be used on the register file as

well. This is enabled by the fact that the register file is

assigned the 32 lowermost Data Space addresses ($00 -

$1F), allowing them to be accessed as though they were

ordinary memory locations.

The I/O memory space contains 64 addresses for CPU

peripheral functions as Control Registers, Timer/Counters,

A/D-converters, and other I/O functions. The I/O Memory

can be accessed directly, or as the Data Space locations

following those of the register file, $20 - $5F.

The AVR uses a Harvard architecture concept - with sepa-

rate memories and buses for program and data. The pro-

gram memory is executed with a two stage pipeline. While

one instruction is being executed, the next instruction is

pre-fetched from the program memory. This concept

enables instructions to be executed in every clock cycle.

The program memory is in-system In-System Programma-

ble Flash memory.

With the relative jump and call instructions, the whole 2K

address space is directly accessed. Most AVR instructions

4

AT90S4414