M69AR048B データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

M69AR048B Datasheet PDF : 29 Pages

| |||

M69AR048B

uration data is written. The data of the fourth cycle

must be all 0s, and the data of the fifth cycle is the

Power-Down Configuration data (see Table

5., Power-Down Configuration Data). If the fourth

cycle is written into a different address, the se-

quence is aborted. In the last cycle, a read is made

from the specific Power-Down Configuration ad-

dress (see Table 6., Power-Down Configuration

Addresses). The Power-Down Configuration data

and address must correspond, otherwise the se-

quence is aborted.

When this sequence is performed to take the de-

vice from one Partial Power-Down mode to anoth-

er, the write data may be lost. So, if a Partial

Power-Down mode is used, this sequence should

be performed prior to any normal read or write op-

erations.

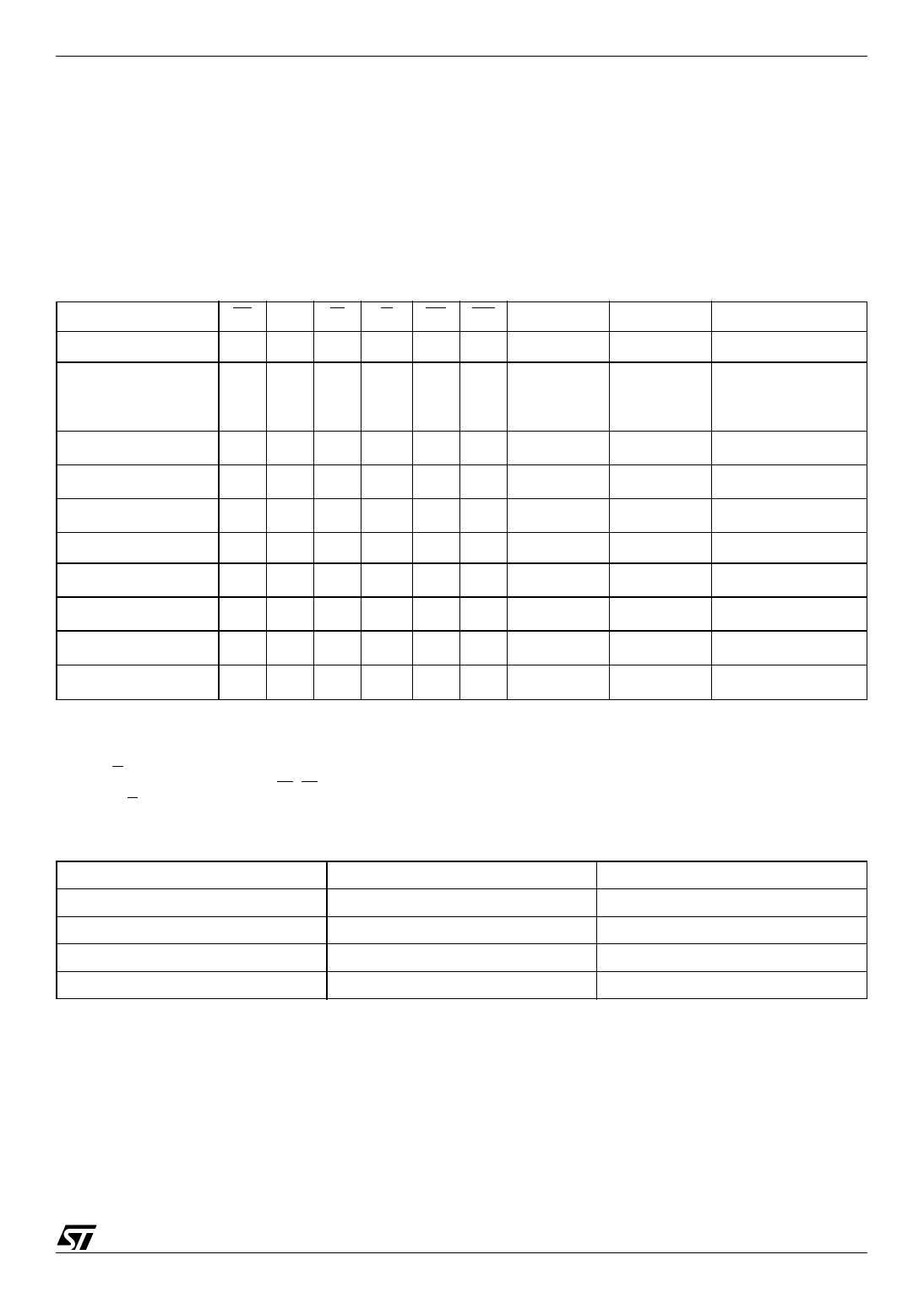

Table 2. Operating Modes

Operation

E1 E2 W G LB UB DQ0-DQ7 DQ8-DQ15

Power

Standby (Deselected) VIH VIH X

X

X

X

Hi-Z

Hi-Z

Standby (ISB)

Power-down (2)

X VIL X

X

X

X

Hi-Z

Hi-Z

Power-Down (ICCPD,

ICCP4, ICCP8 or

ICCP16)

No Read (1)

VIL VIH VIH VIL VIH VIH

Hi-Z

Hi-Z

Output Disable

Lower Byte Read (1) VIL VIH VIH VIL VIL VIH Data Output

Hi-Z

Active (ICC)

Lower Byte Write (1) VIL VIH VIL VIH VIL VIH Data Input

Hi-Z

Active (ICC)

No Write

VIL VIH VIL VIH VIH VIH

Hi-Z

Hi-Z

Output Disable

Upper Byte Read (1) VIL VIH VIH VIL VIH VIL

Hi-Z

Data Output

Active (ICC)

Upper Byte Write (1)

VIL VIH VIL VIH VIH VIL

Hi-Z

Data Input

Active (ICC)

Word Read (1)

VIL VIH VIH VIL VIL VIL Data Output Data Output

Active (ICC)

Word Write (1)

VIL VIH VIL VIH(3) VIL VIL Data Input Data Input

Active (ICC)

Note: X = VIH or VIL.

1. Should not be kept in this logic condition for a period longer than 1µs.

2. Power-Down mode can be entered from Standby state and all DQ pins are in High-Z state. The Power-Down current and data re-

tention depend on the selection of the Power-Down programming.

3. G can be VIL during the Write operation if the following conditions are satisfied:

a. Write pulse is initiated by E1 (E1 Controlled Write timing), or cycle time of the previous operation cycle is satisfied;

b. G stays VIL during the entire Write cycle.

Table 3. Power-Down Modes

Mode

Deep Power-Down (default)

4M Partial Power-Down

8M Partial Power-Down

16M Partial Power-Down

Data Retention

No

4 Mbit

8 Mbit

16 Mbit

Retention Address

N/A

00000h – 3FFFFh

00000h – 7FFFFh

00000h – FFFFFh

9/29