BU-61582 データシートの表示(PDF) - Unspecified

部品番号

コンポーネント説明

メーカー

BU-61582 Datasheet PDF : 48 Pages

| |||

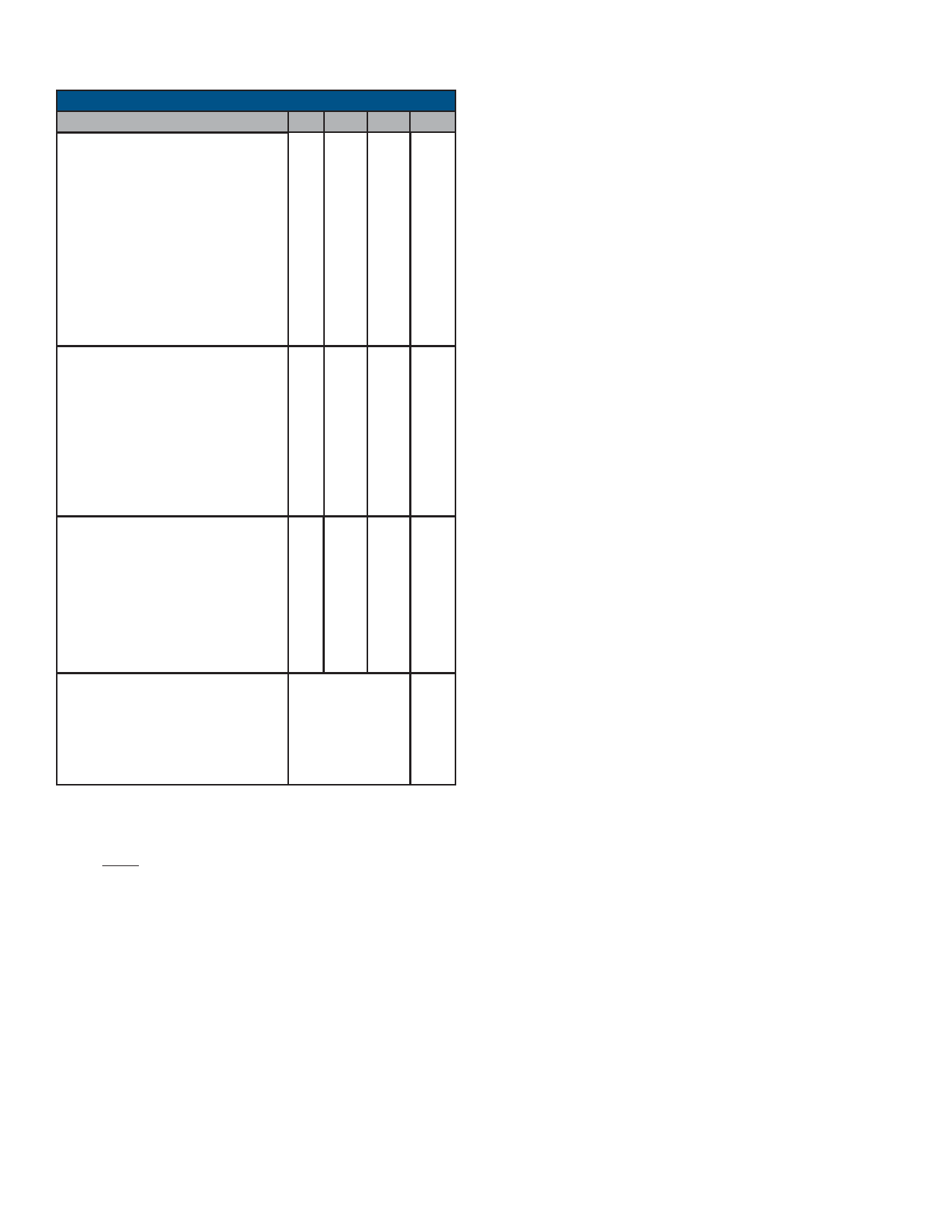

TABLE 1. SP’ACE SERIES SPECIFICATIONS (CONT)

PARAMETER

MIN TYP MAX UNITS

CLOCK INPUT

Frequency

Nominal Value (programmable)

• Default Mode

• Option

Long Term Tolerance

• 1553A Compliance

• 1553B Compliance

Short Term Tolerance,1 second

• 1553A Compliance

• 1553B Compliance

Duty Cycle

• 16 MHz

• 12 MHz

16.0

MHz

12.0

MHz

0.01 %

0.1 %

0.001 %

0.01 %

33

67 %

40

60 %

1553 MESSAGE TIMING

Completion of CPU Write (BC Start-

2.5

µs

to-Start of Next Message)

BC Intermessage Gap (Note 8)

10.5

µs

BC/RT/MT Response Timeout (Note 9)

18.5 nominal

17.5 18.5 19.5 µs

22.5 nominal

21.5 22.5 23.5 µs

50.5 nominal

49.5 50.5 51.5 µs

128.0 nominal

128 129.5 131 µs

Transmitter Watchdog Timeout

668

µs

RT Response Timeout (Note 11)

4 6.5 9

µs

THERMAL

Thermal Resistance, Junction-to-Case,

Hottest Die (θJC)

BU-61582X0

4.6

°C/W

BU-61582X1

7.2

°C/W

BU-61582X2

7.2

°C/W

BU-61582X3/X6

12

°C/W

Operating Junction Temperature

-55

150 °C

Storage Temperature

-65

150 °C

Lead Temperature (soldering, 10 sec.)

+300 °C

PHYSICAL CHARACTERISTICS

Size

70-pin DIP, Flat Pack

J-Lead, Gull Leads

Weight

70-pin DIP, Flat Pack

J-Lead, Gull Leads

1.9 X 1.0 X 0.215 in.

(48.26 x 25.4 x 5.46 (mm)

0.6

oz

(7)

(g)

TABLE 1 NOTES: Notes 1 through 6 are applicable to the Receiver

Differential Resistance and Differential Capacitance specifications:

(1) Specifications include both transmitter and receiver (tied together

internally).

(2) Measurement of impedance is directly between pins TX/RX A(B)

and TX/RX A(B) of the SP'ACE Series hybrid.

(3) Assuming the connection of all power and ground inputs to the

hybrid.

(4) The specifications are applicable for both unpowered and powered

conditions.

(5) The specifications assume a 2 volt rms balanced, differential, sinu-

soidal input. The applicable frequency range is 75 kHz to 1 MHz.

(6) Minimum resistance and maximum capacitance parameters are

guaranteed, but not tested, over the operating range.

(7) Assumes a common mode voltage within the frequency range of dc

to 2 MHz, applied to pins of the isolation transformer on the stub

side (either direct or transformer coupled), referenced to hybrid

ground. Use a DDC recommended transformer or other transformer

that provides an equivalent minimum CMRR.

(8) Typical value for minimum intermessage gap time. Under software

control, may be lengthened to (65,535 µs minus message time), in

increments of 1 µs.

TABLE 1 NOTES (cont)

(9) Software programmable (4 options). Includes RT-to-RT Timeout

(Mid-Parity of Transmit Command to Mid-Sync of Transmitting RT

Status).

(10) For both +5 V logic and transceiver. +5 V for channels A and B.

(11) Measured from mid-parity crossing of Command Word to mid-sync

crossing of RT's Status Word.

INTRODUCTION

DDC’s SP’ACE series of Integrated BC/RT/MT hybrids provide a

complete, flexible interface between a microprocessor and a

MIL-STD-1553A, B Notice 2, McAir, or STANAG 3838 bus,

implementing Bus Controller, Remote Terminal (RT) and Monitor

Terminal (MT) modes. Packaged in a single 1.9 square inch 70-

pin DIP, surface mountable Flat Pack or Gull Lead, the SP’ACE

series contains dual low-power transceivers and

encoder/decoders, complete BC/RT/MT multiprotocol logic,

memory management and interrupt logic, 16K X 16 of shared

static RAM and a direct, buffered interface to a host processor

bus.

The BU-61582 contains internal address latches and bidirection-

al data buffers to provide a direct interface to a host processor

bus. The BU-61582 may be interfaced directly to both 16-bit and

8-bit microprocessors in a buffered shared RAM configuration. In

addition, the SP’ACE may connect to a 16-bit processor bus via

a Direct Memory Access (DMA) interface. The BU-61582

includes 16K words of buffered RAM. Alternatively, the SP’ACE

may be interfaced to as much as 64k words of external RAM in

either the shared RAM or DMA configurations.

The SP’ACE RT mode is multiprotocol, supporting MIL-STD-

1553A, MIL-STD-1553B Notice 2, and STANAG 3838 (including

EFAbus).

The memory management scheme for RT mode provides an

option for separation of broadcast data, in compliance with

1553B Notice 2. Both double buffer and circular buffer options

are programmable by subaddress. These features serve to

ensure data consistency and to off-load the host processor for

bulk data transfer applications.

The SP’ACE series implements three monitor modes: a word

monitor, a selective message monitor, and a combined RT/selec-

tive monitor.

Other features include options for automatic retries and pro-

grammable intermessage gap for BC mode, an internal Time Tag

Register, an Interrupt Status Register and internal command ille-

galization for RT mode.

Data Device Corporation

www.ddc-web.com

4

BU-61582

M-08/04-0