AD74111YRUZ データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

AD74111YRUZ Datasheet PDF : 20 Pages

| |||

AD74111

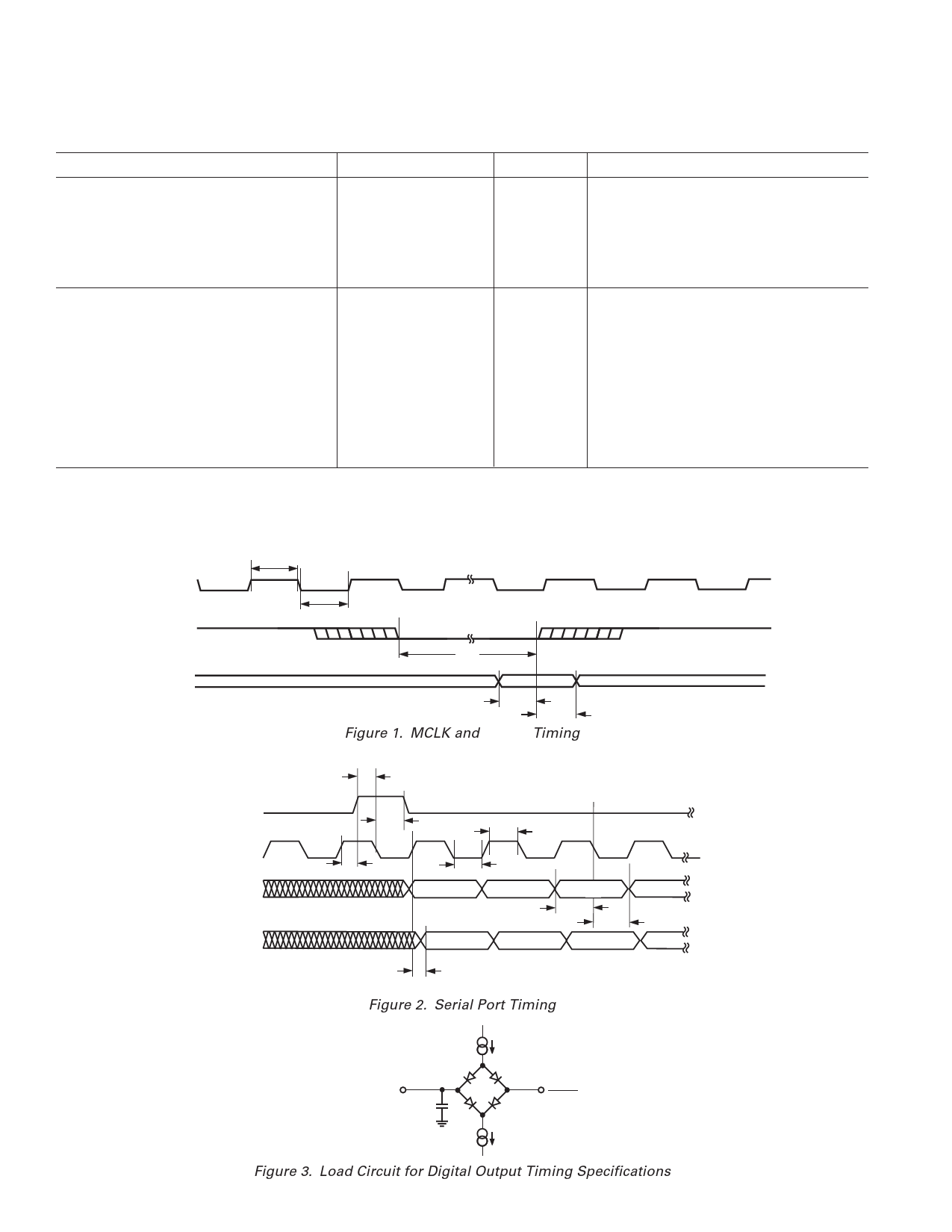

TIMING CHARACTERISTICS (AVDD = 2.5 V ± 5%, DVDD2 = 2.5 V ± 5%, DVDD1 = 3.3 V ± 10%, fMCLK = 12.288 MHz, fS = 48 kHz,

TA = TMIN to TMAX, unless otherwise noted.)

Parameter

MASTER CLOCK AND RESET

tMH

MCLK High

tML

MCLK Low

tRES

RESET Low

tRS

DIN Setup Time

tRH

DIN Setup Time

SERIAL PORT

tCH

DCLK High2

tCL

DCLK Low2

tFD

DFS Delay

tFS

DFS Setup Time

tFH

DFS Hold Time

tDD

DOUT Delay

tDS

DIN Setup Time

tDH

DIN Hold Time

tDT

DOUT Three-State

NOTES

1Determines Master/Slave mode operation.

2Applies in Slave mode only.

3Applies in Master mode only.

4Applies in Multiframe-Sync mode only.

tMH

MCLK

RESET

Min

25

25

10

5

5

20

20

5

15

5

15

tML

Max

5

30

40

Unit

ns

ns

ns

MCLKS

MCLKS

ns

ns

ns

ns

ns

ns

ns

ns

ns

Comments

To RESET Rising Edge1

To RESET Rising Edge1

From DCLK Rising Edge3

To DCLK Falling Edge

From DCLK Falling Edge

From DCLK Rising Edge

To DCLK Falling Edge

From DCLK Falling Edge

From DCLK Rising Edge4

tRES

DIN

tRS

tRH

Figure 1. MCLK and RESET Timing

tFS

DFS

DCLK

DIN

DOUT

tFH

tFD

tCH

tCL

MSB

MSB

MSB–1

MSB–1

MSB–2

tDS

tDH

MSB–2

tDD

Figure 2. Serial Port Timing

100A

IOL

TO OUTPUT

PIN

CL

50pF

100A

IOH

DVDD1

2

Figure 3. Load Circuit for Digital Output Timing Specifications

–4–

REV. 0