AD74111YRUZ データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

AD74111YRUZ Datasheet PDF : 20 Pages

| |||

AD74111

78

74

70

66

62

58

54

84

16

24

32

40

48

SAMPLE RATE – kHz

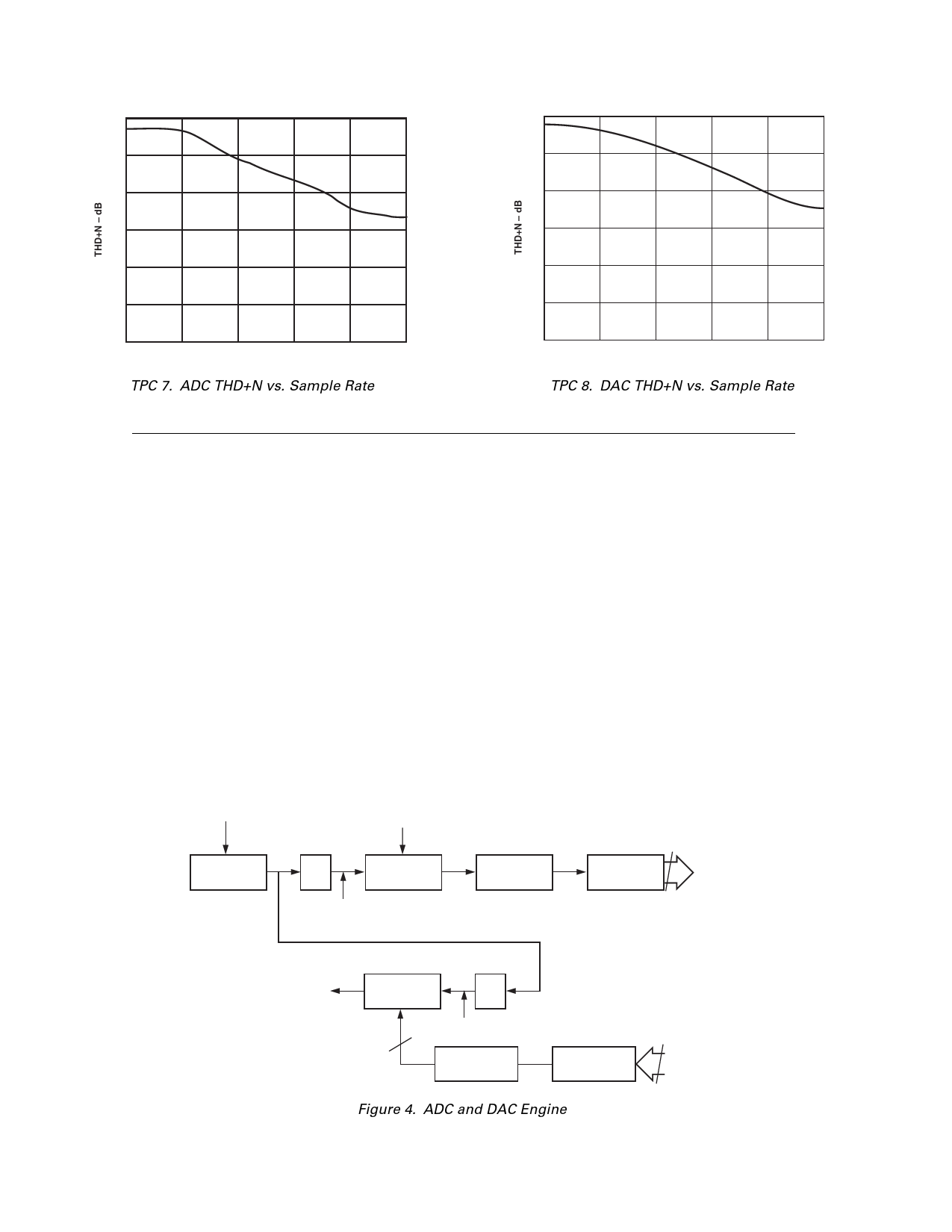

TPC 7. ADC THD+N vs. Sample Rate

90

88

86

84

82

80

78

8

16

24

32

40

48

SAMPLE RATE – kHz

TPC 8. DAC THD+N vs. Sample Rate

FUNCTIONAL DESCRIPTION

General Description

The AD74111 is a 2.5 V mono codec. It comprises an ADC and

DAC channel with single-ended input and output. The ADC

has a programmable gain stage and the DAC has programmable

volume control. Each of these sections is described in further

detail below. The AD74111 is controlled by means of a flexible

serial port (SPORT) that can be programmed to accommodate

many industry standard DSPs and microcontrollers. The AD74111

can be set to operate as a master or slave device. The AD74111

can be set to operate with sample rates of 8 kHz to 48 kHz,

depending on the values of MCLK and the MCLK prescalers.

On-chip digital filtering is provided as part of the DAC and

ADC channels with a low group delay option to reduce the delays

through the filters when operating at lower sample rates. Figure 4

shows a block diagram of the DAC and ADC channel in the

AD74111. Figures 5a and 5b show block diagrams of the filter

arrangements of the ADC and DAC filters.

ADC Section

The AD74111 contains a multibit sigma-delta ADC. The ADC

has a single input pin with additional pins for decoupling/filter

capacitors. The ADC channel has an independent input amplifier

gain stage that can be programmed in steps of 3 dB, from 0 dB

to 12 dB. The input amplifier gain settings are set by program-

ming the appropriate bits in Control Register E. The ADC can

also be muted under software control. The AD74111 input

channel employs a multibit sigma-delta conversion technique that

provides a high resolution output with system filtering imple-

mented on-chip. Sigma-delta converters employ a technique

known as oversampling, where the sampling rate is many times

the highest frequency of interest. In the case of the AD74111,

the oversampling ratio is 64 and a decimation filter is used to

reduce the output to standard sample rates. The maximum sample

rate is 48 kHz.

MCLK

ADC

INPUT

PRESCALERS

(/1 to /12)

/4

⌺-⌬ ADC

MODULATOR

ADC MODULATOR

CLOCK

SINC FILTER

(/8)

DECIMATOR

(/8)

ADC

DATA

16-/20-/24-

BITS

DAC O/P

⌺-⌬ DAC

MODULATOR

/2

5 BITS

DAC MODULATOR

CLOCK

INTERPOLATOR

(؋ 16)

INTERPOLATOR

(؋ 8)

Figure 4. ADC and DAC Engine

DAC

DATA

16-/20-/24-

BITS

–8–

REV. 0