24WC16 データシートの表示(PDF) - Catalyst Semiconductor => Onsemi

部品番号

コンポーネント説明

メーカー

24WC16 Datasheet PDF : 10 Pages

| |||

CAT24WC01/02/04/08/16

Selective Read

Selective READ operations allow the Master device to

select at random any memory location for a READ

operation. The Master device first performs a ‘dummy’

write operation by sending the START condition, slave

address and byte address of the location it wishes to

read. After the CAT24WC01/02/04/08/16 acknowledge

the word address, the Master device resends the START

condition and the slave address, this time with the R/W

bit set to one. The CAT24WC01/02/04/08/16 then

responds with its acknowledge and sends the 8-bit byte

requested. The master device does not send an

acknowledge but will generate a STOP condition.

Sequential Read

The Sequential READ operation can be initiated by

either the immediate Address READ or Selective READ

operations. After the 24WC01/02/04/08/16 sends initial

8-bit byte requested, the Master will respond with an

acknowledge which tells the device it requires more

data. The CAT24WC01/02/04/08/16 will continue to

output an 8-bit byte for each acknowledge sent by the

Master. The operation is terminated when the Master

fails to respond with an acknowledge, thus sending the

STOP condition.

The data being transmitted from the CAT24WC01/02/

04/08/16 is outputted sequentially with data from address

N followed by data from address N+1. The READ

operation address counter increments all of the

CAT24WC01/02/04/08/16 address bits so that the entire

memory array can be read during one operation. If more

than the E (where E = 255 for 24WC02, 511 for 24WC04,

1023 for 24WC08, and 2047 for 24WC16) bytes are read

out, the counter will “wrap around” and continue to clock

out data bytes. If N = E (where E = 127 for the

CAT24WC01) the counter will not 'wrap around'.

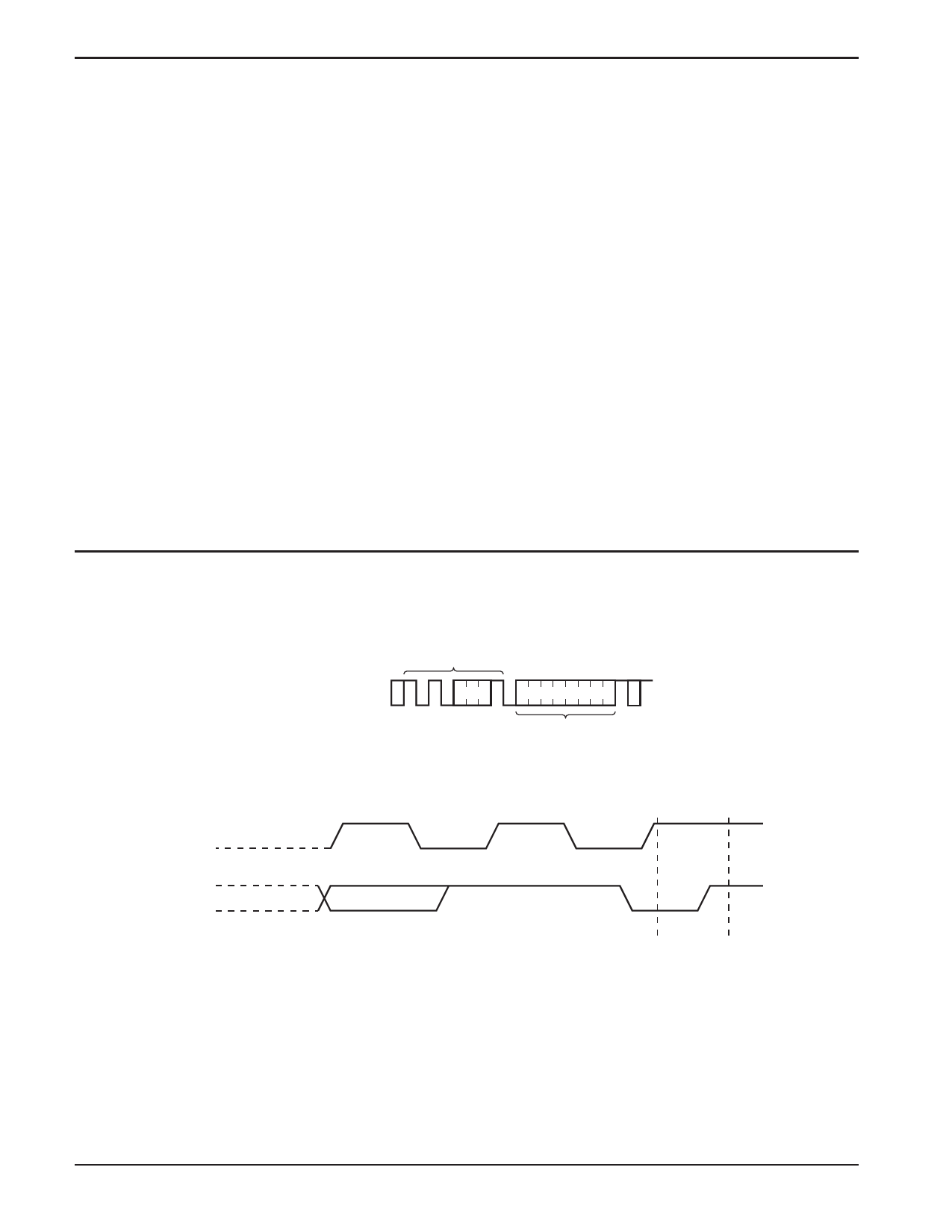

Figure 8. Immediate Address Read Timing

S

T

S

BUS ACTIVITY: A

SLAVE

T

MASTER R ADDRESS

O

T

P

SDA LINE S

P

A

N

C

DATA

O

K

A

C

K

SCL

8

9

SDA

8TH BIT

DATA OUT

NO ACK

STOP

5020 FHD F10

Doc. No. 1022, Rev. J

8