28F256L30 „Éá„Éľ„āŅ„ā∑„Éľ„Éą„ĀģŤ°®Á§ļÔľąPDFÔľČ - Numonyx -> Micron

ťÉ®ŚďĀÁē™ŚŹ∑

„ā≥„É≥„ÉĚ„Éľ„Éć„É≥„ÉąŤ™¨śėé

„É°„Éľ„āę„Éľ

28F256L30 Datasheet PDF : 102 Pages

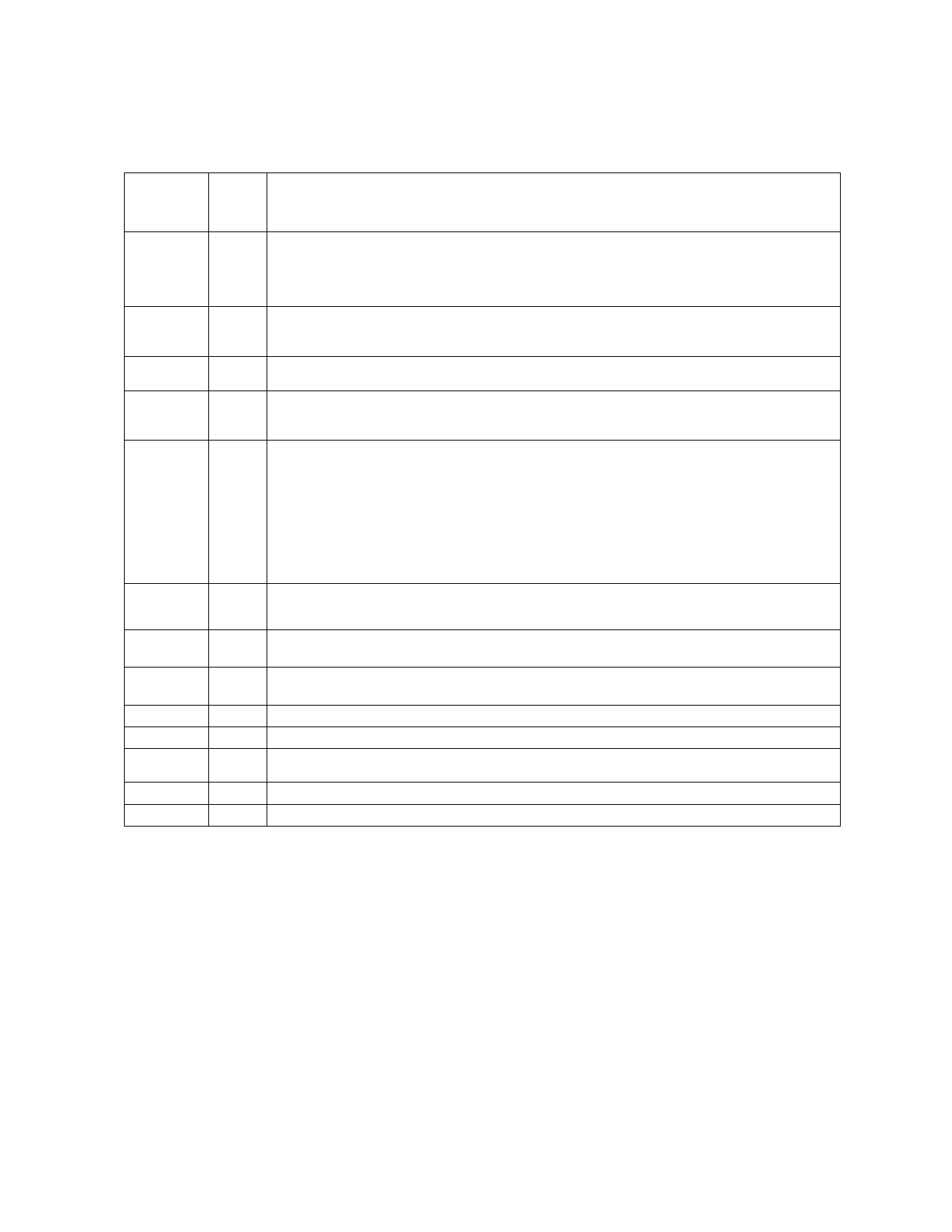

| |||

Numonyx‚ĄĘ StrataFlash¬ģ Wireless Memory (L30)

Table 2:

WP#

ADV#

R-UB#

R-LB#

RST#

P-Mode

VPP,

VPEN

F1-VCC

F2-VCC

S-VCC

P-VCC

VCCQ

VSS

RFU

DU

NC

Device Signal Descriptions for 128/0 and 256/0 SCSP (Sheet 2 of 2)

Input

FLASH WRITE PROTECT: Low-true; WP# enables/disables the lock-down protection mechanism of

the selected flash die. WP#-low enables the lock-down mechanism - locked down blocks cannot be

unlocked with software commands. WP#-high disables the lock-down mechanism, allowing locked

down blocks to be unlocked with software commands.

Input

FLASH ADDRESS VALID: Active-low input. During synchronous read operations, addresses are

latched on the rising edge of ADV#, or on the next valid CLK edge with ADV# low, whichever occurs

first.

In asynchronous mode, the address is latched when ADV# going high or continuously flows through if

ADV# is held low.

Input

RAM UPPER / LOWER BYTE ENABLES: Low-true; During RAM reads, R-UB#-low enables the RAM

high order bytes on DQ[15:8], and R-LB#-low enables the RAM low-order bytes on DQ[7:0].

Treat this signal as NC (No Connect) for this device.

Input FLASH RESET: Low-true; RST#-low initializes flash internal circuitry and disables flash operations.

RST#-high enables flash operation. Exit from reset places the flash in asynchronous read array mode.

Input

PSRAM MODE: Low-true; P-MODE is used to program the configuration register, and enter/exit low

power mode.

Treat this signal as NC (No Connect) for this device.

Power/

Input

FLASH PROGRAM / ERASE POWER: A valid voltage on this pin allows erasing or programming.

Memory contents cannot be altered when VPP ‚ȧ VPPLK. Block erase and program at invalid VPP voltages

should not be attempted.

Set VPP = VCC for in-system program and erase operations. To accommodate resistor or diode drops

from the system supply, the VIH level of VPP can be as low as VPPLmin. VPP must remain above VPPLmin

to perform in-system flash modification. VPP may be 0 V during read operations.

VPPH can be applied to main blocks for 1000 cycles maximum and to parameter blocks for 2500 cycles

maximum. VPP can be connected to VPPH for a cumulative total not to exceed 80 hours. Extended use

of this pin at VPPH may reduce block cycling capability

VPEN (Erase/Program/Block Lock Enables) is not available for L30 products.

Power

Power

FLASH LOGIC POWER: F1-VCC supplies power to the core logic of flash die #1; F2-VCC supplies

power to the core logic of flash die #2. Write operations are inhibited when VCC ‚ȧ VLKO. Device

operations at invalid VCC voltages should not be attempted.

SRAM Power Supply: Supplies power for SRAM operations.

Treat this signal as NC (No Connect) for this device.

PSRAM Power SUpply: Supplies power for PSRAM operations.

Power

Treat this signal as NC (No Connect) for this device.

Power Flash I/O Power: Supply power for the input and output buffers.

Power Ground: Connect to system ground. Do not float any VSS connection.

Reserved for Future Use: Reserve for future device functionality/ enhancements. Contact Numonyx

‚ÄĒ

regarding their future use.

‚ÄĒ

Do Not Use: Do not connect to any other signal, or power supply; must be left floating.

‚ÄĒ

No Connect: No internal connection; can be driven or floated.

4.3

Memory Map

See Table 3, ‚ÄúTop Parameter Memory Map, 128-Mbit‚ÄĚ on page 20 and Table 5, ‚ÄúBottom

Parameter Memory Map, 128-Mbit‚ÄĚ on page 21. The memory array is divided into

multiple partitions; one parameter partition and several main partitions:

‚ÄĘ 128-Mbit device. This contains sixteen partitions: one 8-Mbit parameter partition,

fifteen 8-Mbit main partitions.

‚ÄĘ 256-Mbit device. This contains sixteen partitions: one 16-Mbit parameter partition,

fifteen 16-Mbit main partitions.

November 2007

Order Number: 251903-11

Datasheet

19