29C516E データシートの表示(PDF) - Atmel Corporation

部品番号

コンポーネント説明

メーカー

29C516E Datasheet PDF : 17 Pages

| |||

29C516E

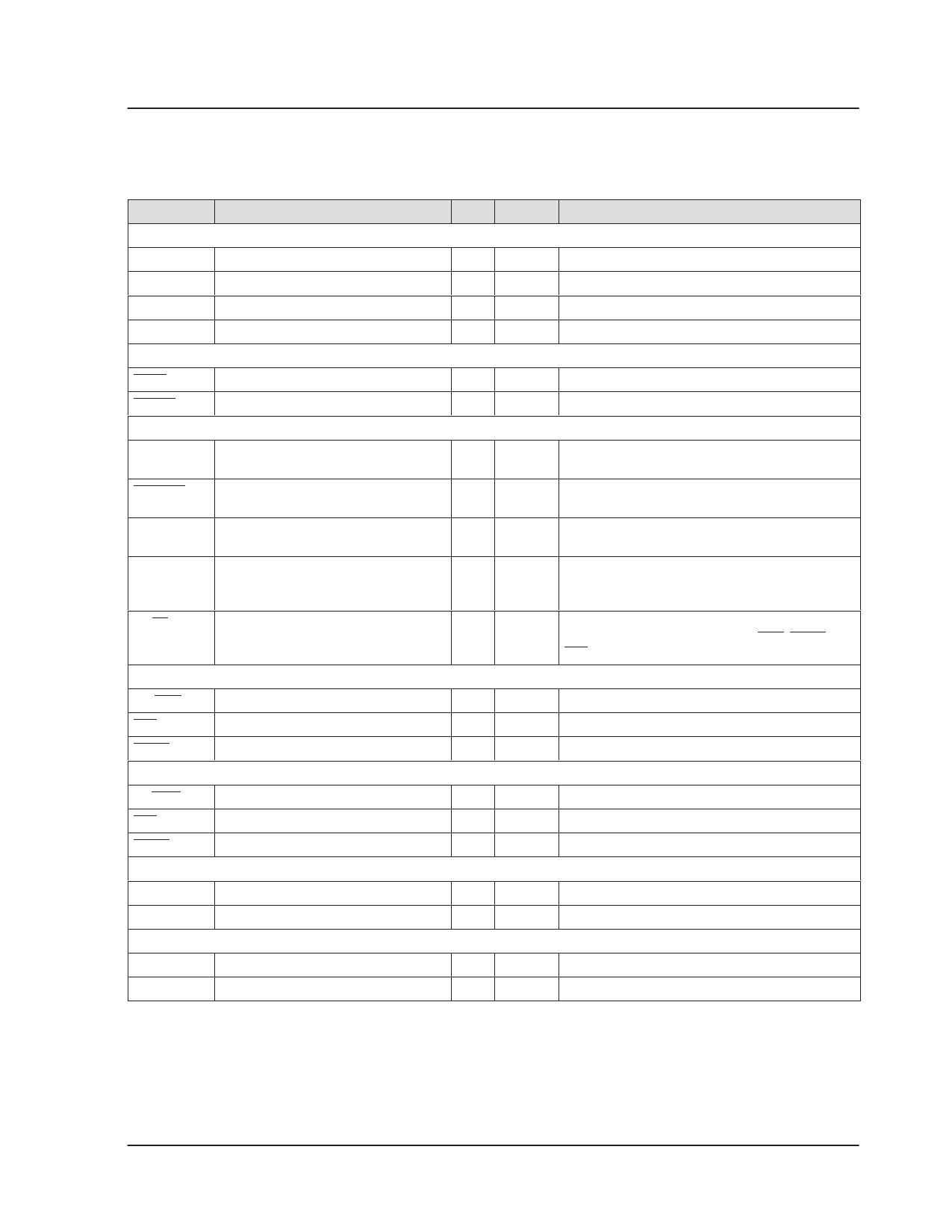

3.4. Pin Description

Table 1:

Name

Pin Description

Buses

U1D[0..15]

U2D[0..15]

53,49..47,45..42,40..37,35..33,28

23..20,18..15,13..10,8..5

ΜD[0..15]

59..62,64..67,69..72,74..77

ΜC[0..7]

83..86,88..91

Error Flags

CERR

26

NCERR

25

General Control Signals

CORRECT 98

SYNCHK

97

N22

27

TRANS

96

U2/U1

95

User 1 Control Signals

RD/WRT

55

EN1

56

MEM1

57

User 1 Control Signals

RD/WR2

99

EN2

94

MEM2

3

Power (Buffers)

VCCB

GNDB

Power (Core)

9,19,32,41,54,63,73,87

4,14,24,36,46,58,68,78,92

VCCC

100

GNDC

93

* Pull–up buffers

I/O Active

Description

I/O* High

I/O* High

I/O* High

I/O* High

User 1 Data Bus

User 2 Data Bus

Memory Data Bus

Memory Check–bit Bus

O

Low

O

Low

Correctable Error

Uncorrectable Error

I* High

I* Low

I* High

I* H/L

I* H/L

When active, the EDAC is in CORRECT mode. If low,

the EDAC is in DETECT mode.

Selects the Syndrome bits (high byte) and the Check–bits

(low byte) to be driven on the selected User Data Bus.

When active, the EDAC uses 6 check–bits. If low, the

EDAC uses 8 check–bits in memory read.

Selects the Data path to be used. If high, the EDAC

access the memory, if low, the EDAC access the transfer

buffer.

Selects who is the master of User 1 and User 2. The

master is responsible for applying RD/WRx, MEMx, and

ENx signals in a correct way.

I* H/L

I* Low

I* Low

User 1 Read/Write signal

User 1 Output Enable

User 1 Memory Select

I* H/L

I*

Low

I*

Low

User 2 Read/Write signal

User 2 Output Enable

User 2 Memory Select

I

–

Buffers supply (5 V nominal)

I

–

Buffers 0 V nominal reference

I

–

Core supply (5 V nominal)

I

–

Core 0 V reference

4

Rev. E (03 2007)