73S8014R データシートの表示(PDF) - Teridian Semiconductor Corporation

部品番号

コンポーネント説明

メーカー

73S8014R Datasheet PDF : 29 Pages

| |||

73S8014R Data Sheet

DS_8014R_012

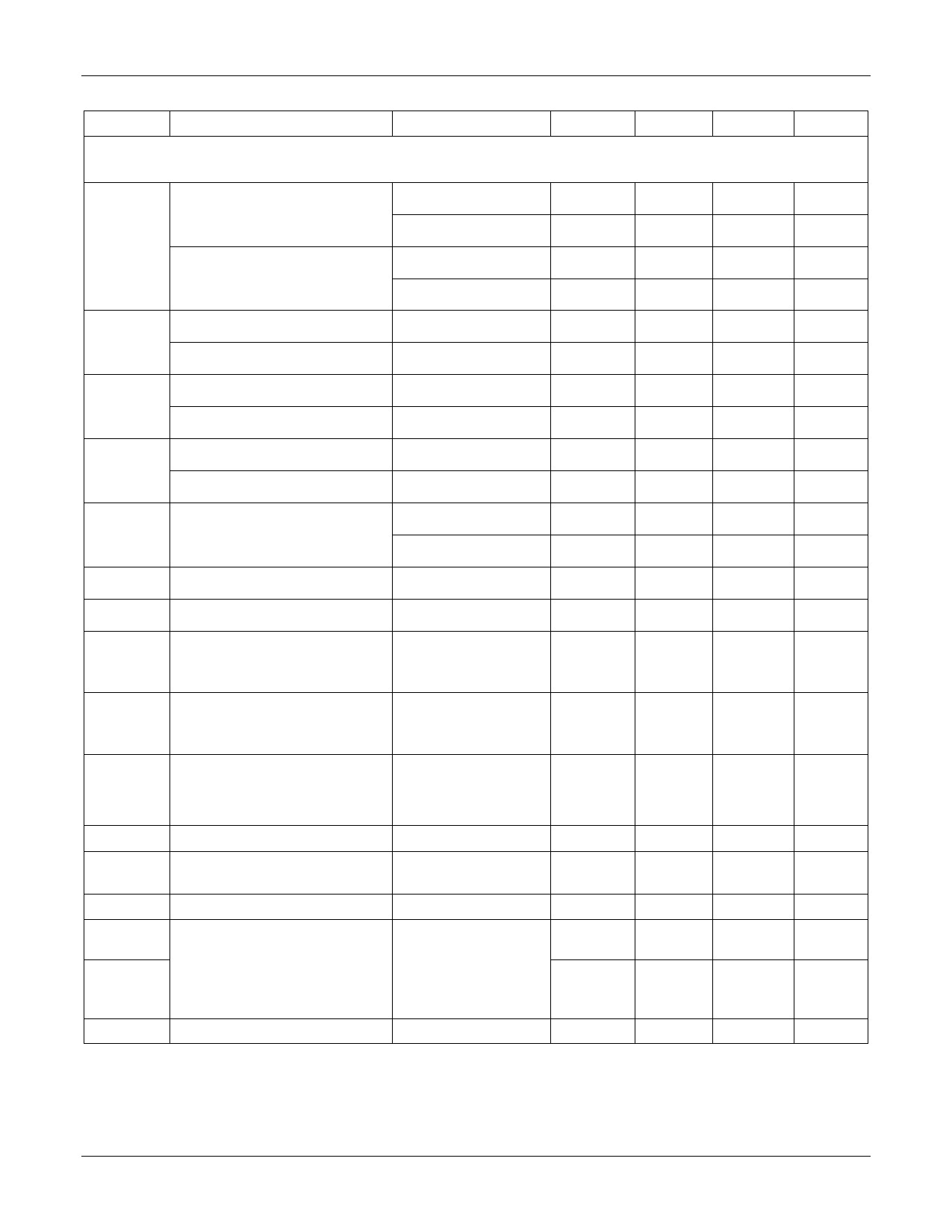

Symbol

Parameter

Condition

Min

Interface Requirements – Data Signals: I/Oand host interfaces: I/OUC.

ISHORTL, ISHORTH, and VINACT requirements do not pertain to I/OUC.

Output level, high (I/O)

VOH

Output level, high (I/OUC)

IOH =0

IOH = -40μA

IOH =0

IOH = -40μA

0.9 VCC

0.75 VCC

0.9 VDD

0.75 VDD

Output level, low (I/O)

VOL

Output level, low (I/OUC)

IOL=1mA

Input level, high (I/O)

VIH

Input level, high (I/OUC)

0.6 VCC

1.8

Input level, low (I/O)

VIL

Input level, low (I/OUC)

-0.15

-0.3

VINACT

ILEAK

IIL

ISHORTL

ISHORTH

tR, tF

Output voltage when outside

of session

Input leakage

Input current, low

Short circuit output current

Short circuit output current

Output rise time, fall times

IOL = 0

IOL = 1mA

VIH = VCC

VIL = 0

For output low,

shorted to VCC

through 33 Ω

For output high,

shorted to ground

through 33 Ω

CL = 80pF, 10% to

90%.

Nom

Max

VCC+0.1

VCC+0.1

VDD+0.1

VDD+0.1

0.15 VCC

0.3

VCC+0.30

VDD + 0.3

0.2 VCC

0.8

0.1

0.3

10

0.65

15

15

100

Unit

V

V

V

V

V

V

V

V

V

V

V

V

μA

mA

mA

mA

ns

tIR, tIF

Input rise, fall times

RPU

Internal pull-up resistor

Output stable for

>400ns

8

FDMAX

Maximum data rate

TFDIO

TRDIO

Delay, I/O to I/OUC,

60

I/OUC to I/O, (respectively

Edge from master to

falling edge to falling edge

slave, measured at

and rising edge to rising

50%

edge)

CIN

Input capacitance

1

μs

11

14

kΩ

1

MHz

100

200

ns

15

ns

10

pF

10

Rev. 1.0