75N43102 データシートの表示(PDF) - Integrated Device Technology

部品番号

コンポーネント説明

メーカー

75N43102 Datasheet PDF : 3 Pages

| |||

Network Search Engine 32K x 72 Entries

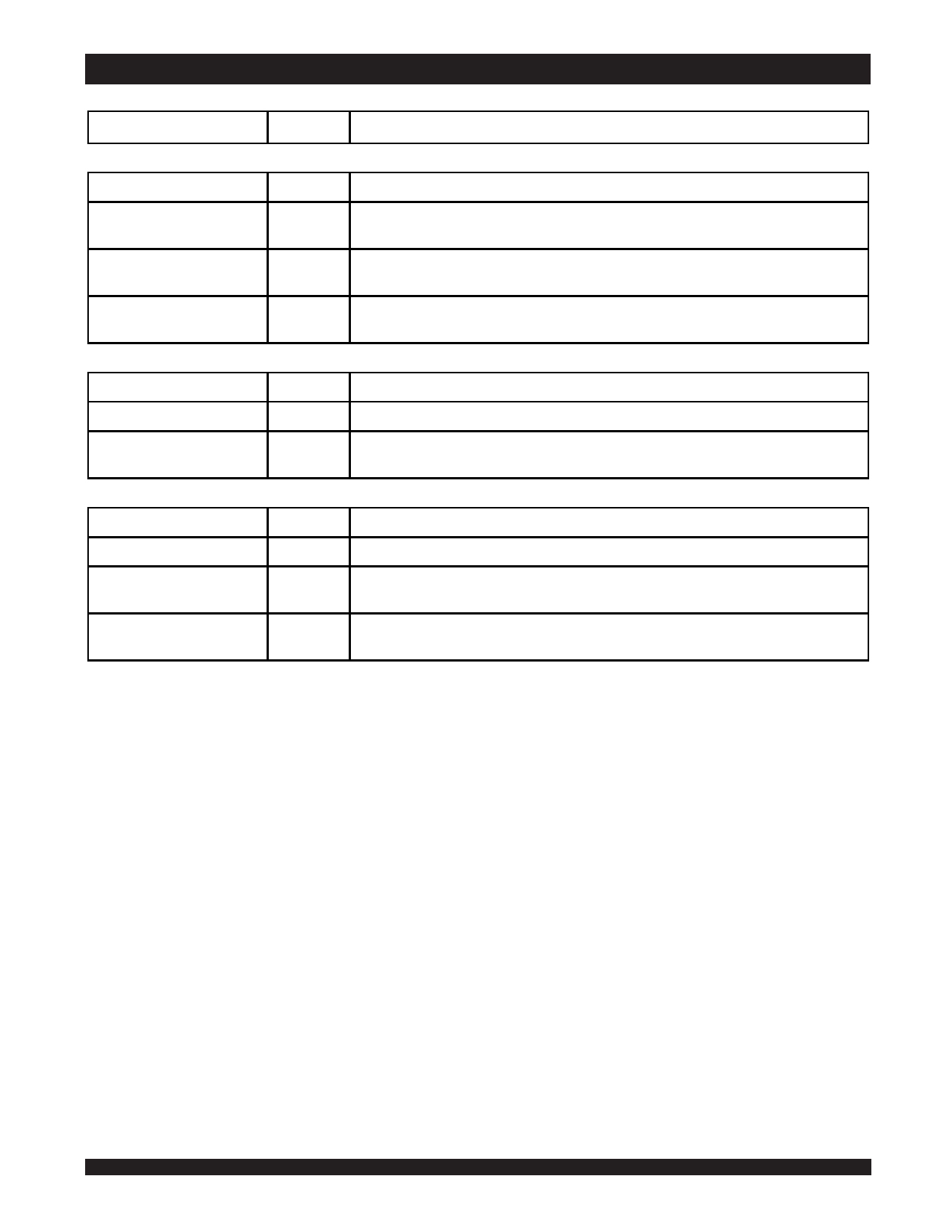

Signal Descriptions

Datasheet Brief 75N43102

Pin Function

I/O Description

NSE Buses:

Request Strobe

Input This input sig nifies a valid input request and signals the start of an NSE operation cycle.

Command Bus

Input

This defines the instruction to be performed by the NSE and selects a global mask

register.

Request Data Bus

Input/Output The Request Data Bus is a multiplexed address/data bus used to perform reads (and

Three State writes) from (to) the NSE, and to present search data for lookups.

Index Bus

Output This bus is used to drive the Lookup result information directly to the NSE's ASIC/FPGA.

Three State The Index Bus contains the encoded location at which the compare was found.

Clock and Initialization:

Clock Input

Input All inputs and outputs are referenced to the positive edge of this clock.

Clock Phase Enable

Input This signal is used to generate an internal clock at ½ the frequency of the input clock.

Reset

Input

This pin will fo rce all outputs to a high impedence condition, as well as clearing the NSE

enable bit.

Depth Expansion:

Configuration

Input Configures the De vice ID at power up.

Configuration

Output Configures the De vice ID at power up.

Match

Input

Input

The Match Input signal is driven by the upstream Match Output signal. This indicates to the

down stream NSE that a hit in the higher priority NSE has occurred.

Match

Output

Output

The Match Output signal sig nifies that a match has occurred in the NSE. The signal is fed

into the Match Input line of the lower priority NSE.

6435 tbl 01

6.432