78Q2120C データシートの表示(PDF) - Teridian Semiconductor Corporation

部品番号

コンポーネント説明

メーカー

78Q2120C Datasheet PDF : 35 Pages

| |||

78Q2120C

10/100BASE-TX

Transceiver

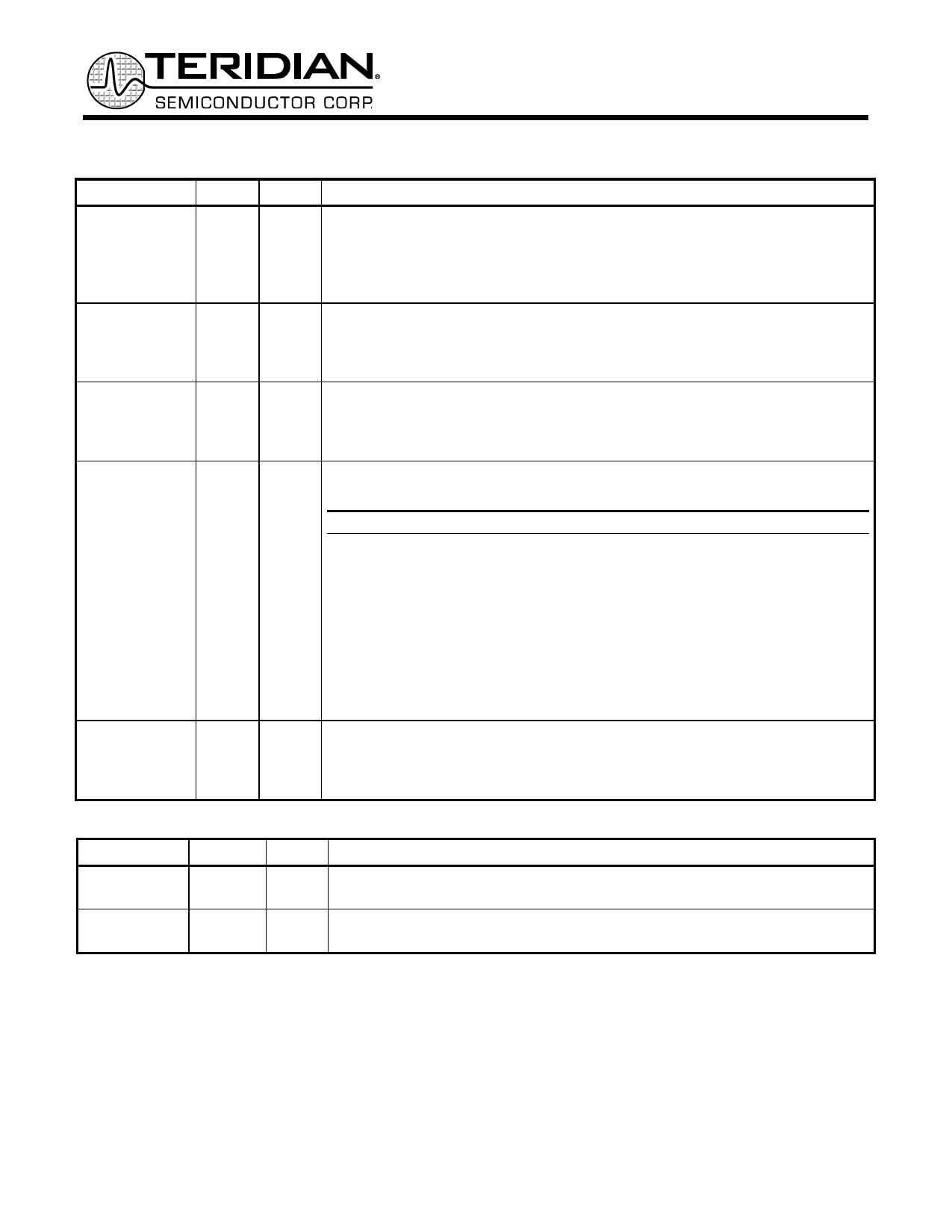

CONTROL AND STATUS (CONTINUED)

NAME

ISO

ISODEF

ANEGA

TECH[2:0]

PIN

2

1

47

44-46

TYPE

CI

CI

CI

CI

DESCRIPTION

ISOLATE: When set to logic one, the 78Q2120C will present a high

impedance on its MII output pins. This allows for multiple chips to be

attached to the same MII interface. When the 78Q2120C is isolated, it still

responds to management transactions. This high impedance state can also

be achieved using the ISO bit in the MII register (MR0.10).

ISOLATE DEFAULT: This pin determines the power-up/reset default of the

ISO bit (MR0.10). If it is connected to VCC, the ISO bit will have a default

value of ‘1’. Otherwise, the bit defaults to ‘0’. When this signal is tied to VCC,

it allows multiple chips to be connected to the same MII interface.

AUTO-NEGOTIATION ABILITY: Connect to logic high to enable the auto-

negotiation function. When connected to logic low, the auto-negotiation logic

is disabled and manual technology selection is done through TECH[2:0] pins.

This pin is reflected as the ANEGA bit in MR1.3.

TECHNOLOGY ABILITY/SELECT: TECH[2:0] sets the technology ability of

the chip which is reflected in MR0.13,8, MR1.14:11 and MR4.12:5.

RPTR

TECH[2:0]

Technology Ability

111

Both 10BASE-T and 100BASE-TX, and

Both half and full duplex

000

None

001

10BASE-T, half duplex

010

100BASE-TX, half duplex

011

Both 10BASE-T and 100BASE-TX, half duplex only

100

None

101

10BASE-T Both half and full duplex

110

100BASE-TX Both half and full duplex

50

CID REPEATER MODE: When pulled high, this pin puts the chip into repeater

mode. In this mode, full duplex is prohibited, CRS responds to receive activity

only. In 10BASE-T mode, the SQE test function is disabled. This mode can

also be enabled by setting bit MR16.15

MDI (MEDIA DEPENDENT INTERFACE)

NAME

TXOP/N

RXIP/N

PIN

61,62

52,51

TYPE

A

A

DESCRIPTION

TRANSMIT OUTPUT POSITIVE/NEGATIVE: Transmitter differential outputs

for both 10BASE-T and 100BASE-TX operation.

RECEIVE INPUT POSITIVE/NEGATIVE: Receiver differential inputs for

both 10BASE-T and 100BASE-TX operation.

Page: 8 of 35

© 2009 Teridian Semiconductor Corporation

Rev 1.3