82574L データシートの表示(PDF) - Intel

部品番号

コンポーネント説明

メーカー

82574L Datasheet PDF : 472 Pages

| |||

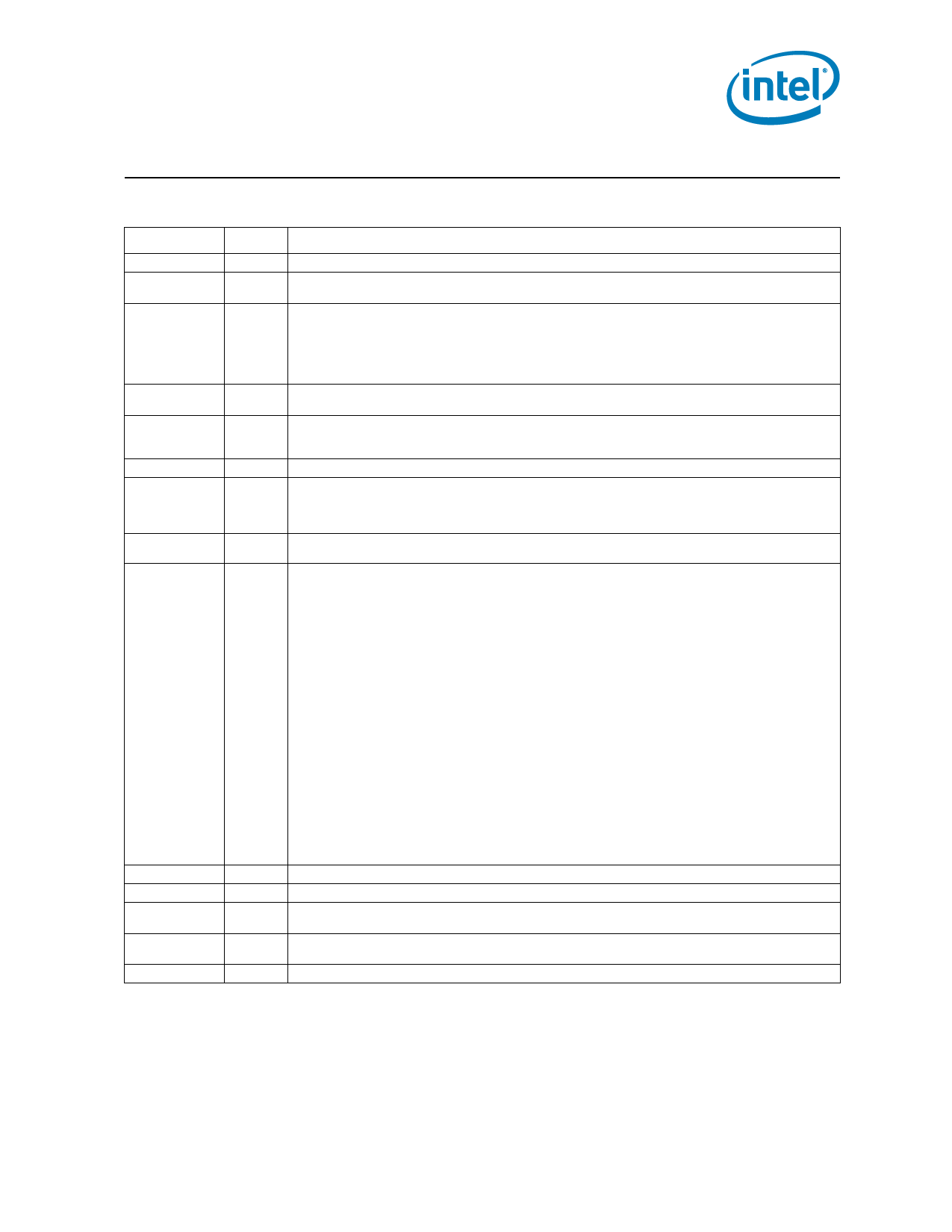

Datasheet—82574 GbE Controller

Revision History

Date

April 2009

February 2009

December 2008

October 2008

August 2008

June 2008

February 2008

February 2008

January 2008

November 2007

October 2007

August 2007

July 2007

June 2007

Revision Description

2.5

• Updated sections 4.5.2, 7.1, 10.2.2.15, 12.6, 13.5.1, and 13.5.5.4.

2.4

• Updated sections 6.3.1.3, 10.2.3.11, and 10.2.8.8.

• Updated table 66.

• Added section 8.12.2.3 - Set Intel Management Control Formats.

• Added section 8.12.3.4 - Get Intel Management Control Formats.

2.3

• Added section 10.2.3.12 - 3GPIO Control Register 2 - GCR2.

• Updated section 13.1.4 - PCIe Routing.

• Updated section 13.10 - Added “The XOR tree is output on the LED1 pin”.

• Updated table 97 - Schematic Checklist.

2.2

• Changed PCIe Rev. 2.0 (2.5 GHz) x1 to PCIe Rev. 1.1 (2.5 GHz) x1 in Section 1.0.

• Added multi-drop application connectivity requirements to Section 13.6.1.2.

• Updated title page - changed packet buffer size from 32 KB to 40 KB.

2.1

• Updated section 15 - corrected NC-SI schematic checklist information.

• Updated reference schematics - corrected NC-SI schematic information.

2.0

Initial public release.

• Updated section 5.2.

1.7

• Added a note to Table 31.

• Updated section 13.5.5.13.

• Added 82574IT ordering information.

1.6

• Quick fix provided which added Measured Power Consumption (Section 5.2). This is a temporary patch. Note

that the fix does not appear in the TOC or list of tables yet. This will be corrected next week.

• Changed section 10.2.2.2 bit 31 assignment from 1b to 0b.

• Changed word 0x0F bit 7 bit assignment (1b to 0b).

• Added new Section 14 “Thermal Design Considerations”.

• Updated MNG Mode description (loads from NVM work 0xF instead of word 10.

• Updated the 82574L Resets table.

• Added note “The 82574L requests I/O resources to support pre-boot operation (prior to the allocation of

physical memory base addresses”.

• Updated CAP Offset 0xE4 bit 15 description.

• Updated default values for Uncorrectable Error Severity and Correctable Error Mask registers.

• Updated Figure 52.

• Updated VALUE1 and VALUE2 byte numbers in Section 10.2.8.19.

1.5

• Changed crystal drive level to 300 W.

• Changed all 1.0 V dc references to 1.05 V dc.

• Changed all 1.8 V dc references to 1.9 V dc.

• Deleted “Default value of 0x5F20 and 0x5F28 are loaded from the NVM at power up" from the FFLT register

description.

• Added a note for EITR that in 10/100 Mb/s mode, the interval time is multiplied by four.

• Updated the type and internal/external PU/PD for NC-SI pins.

• Updated the NVMT pinout description.

• Updated MNG_Mode to be loaded from NVM word 0x0F (instead of NVM word 0x10).

• Updated default values for Uncorrectable Error Severity and Correctable Error Mask registers.

• Updated section 9.1.6.1.7. Where applicable, changed milliseconds to micro seconds (bits 14:12 and 17:15).

• Removed WUPL register information.

• Noted that manageability can be supported with a 32 Kb EEPROM.

1.1

• Updated NVMT symbol description in Section 2.3.4, Table 10.

1.0

• Updated Sections 2, 3, 4, 5, 9, 12, and 13; as indicated by the change bars in the left margin.

0.7

• Updated Sections 2, 3, 5, 6, 8, 10, and 12.

• Added Sections 13, 14, 15, and 16.

0.6

• Added Section 12.0 “Electrical Specifications”.

• Updated Section 2.0 “Pin Interface”.

0.5

Initial release (Intel Confidential).

9