AD9898 データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

AD9898 Datasheet PDF : 52 Pages

| |||

AD9898

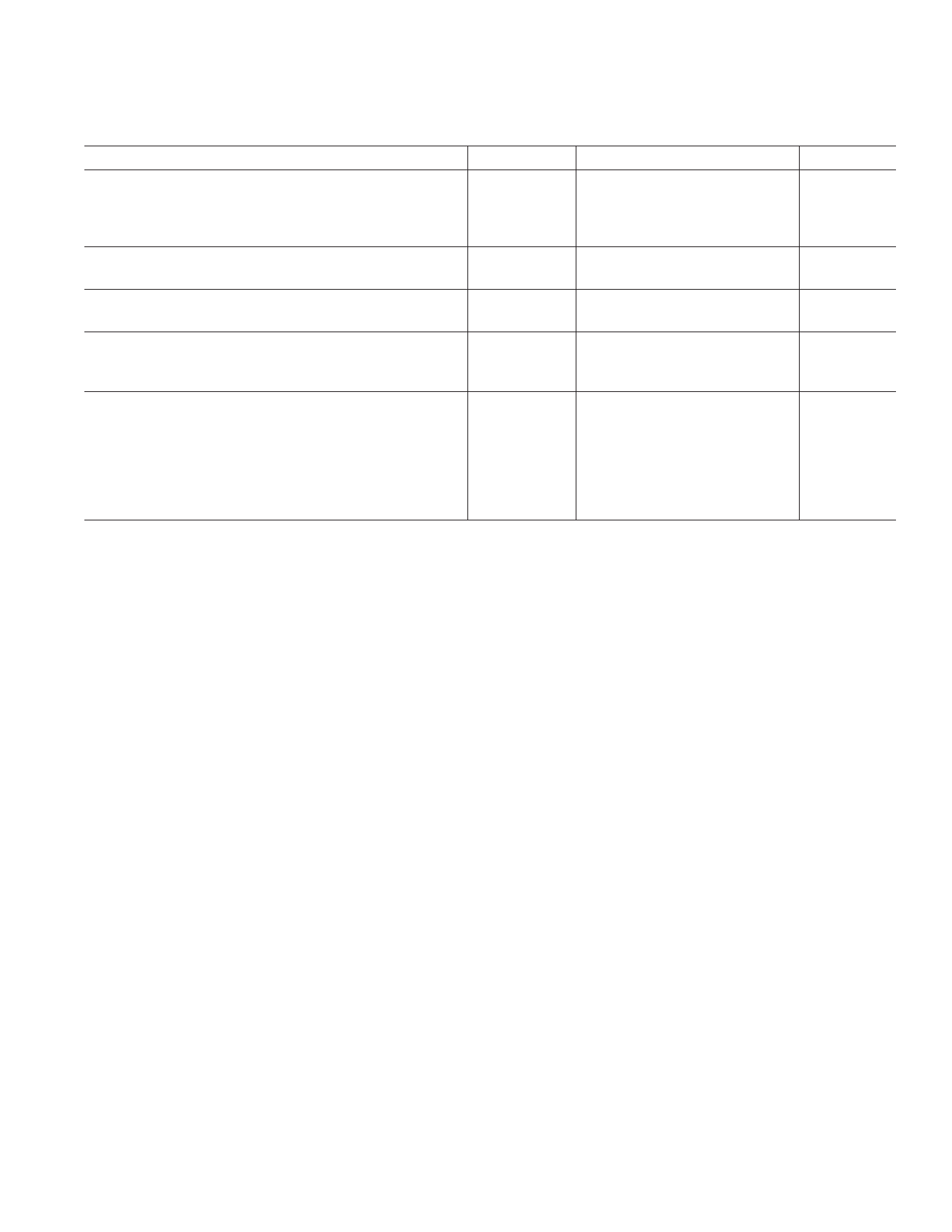

TIMING SPECIFICATIONS (CL = 20 pF, AVDD = DVDD = DRVDD = 3.0 V, fCLI = 20 MHz, unless otherwise noted.)

Parameter

Symbol

Min

Typ

Max Unit

MASTER CLOCK, CLI

CLI Clock Period

CLI High/Low Pulsewidth

Delay from CLI Rising Edge to Internal Pixel Position 0

AFE CLAMP PULSES*

CLPOB Pulsewidth

tCONV

tCLIDLY

50

20

25

6

4

10

ns

ns

ns

Pixels

AFE SAMPLE LOCATION* (See Figure 13)

SHP Sample Edge to SHD Sample Edge

DATA OUTPUTS (See Figure 15)

Output Delay from DCLK Rising Edge

Pipeline Delay from SHP/SHD Sampling

tS1

20

25

tOD

9

9

Pixels

ns

Cycles

SERIAL INTERFACE (See Figures 7 and 8)

Maximum SCK Frequency

SL to SCK Setup Time

SCK to SL Hold Time

SDATA Valid to SCK Rising Edge Setup

SCK Falling Edge to SDATA Valid Hold

SCK Falling Edge to SDATA Valid Read

*Parameter is programmable.

Specifications subject to change without notice.

fSCLK

10

tLS

10

tLH

10

tDS

10

tDH

10

tDV

10

MHz

ns

ns

ns

ns

ns

REV. 0

–5–