AD9992 データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

AD9992 Datasheet PDF : 92 Pages

| |||

AD9992

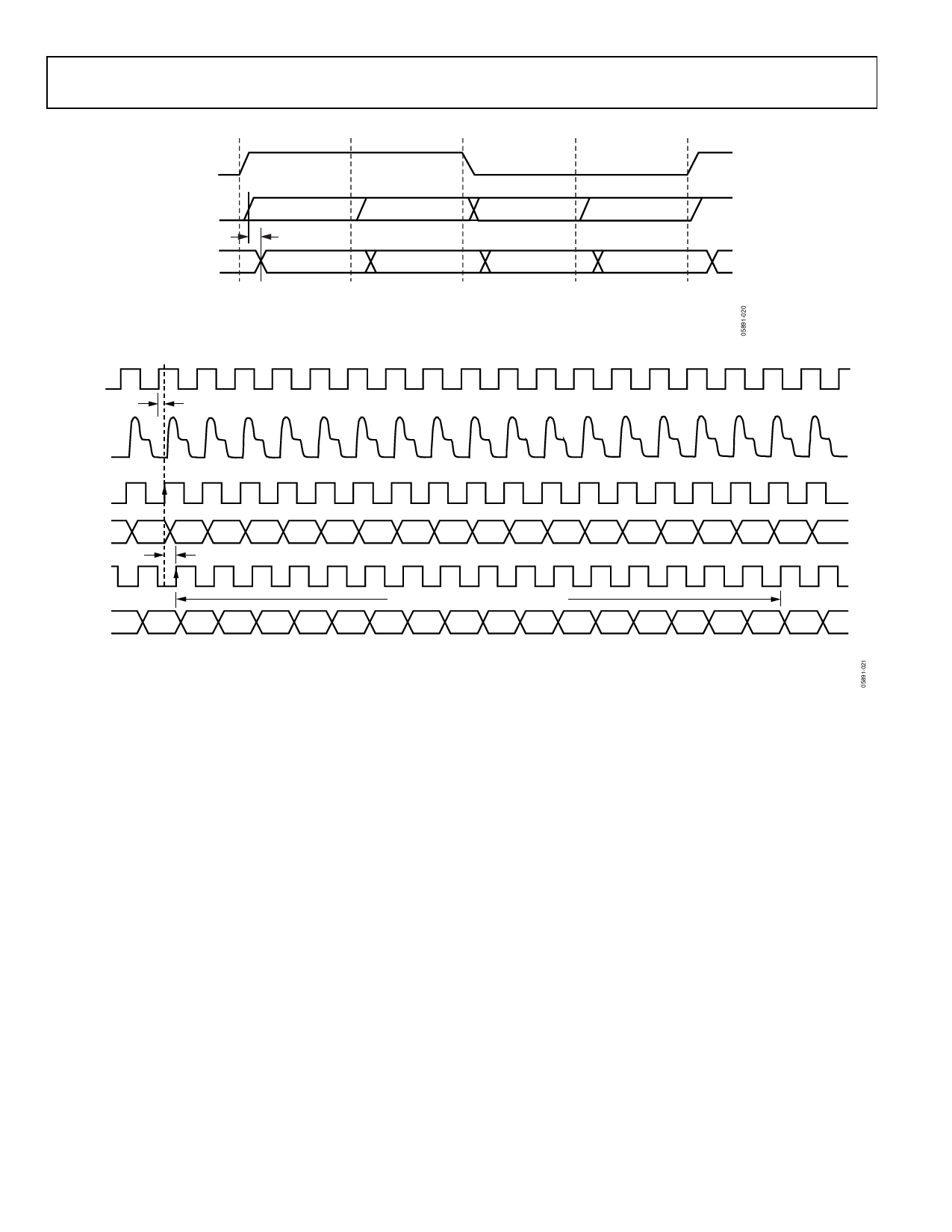

P[0]

PIXEL

PERIOD

P[16]

P[32]

P[48]

P[64] = P[0]

DCLK

tOD

DOUT

NOTES

1. DATA OUTPUT (DOUT) AND DCLK PHASE ARE ADJUSTABLE WITH RESPECT TO THE PIXEL PERIOD.

2. WITHIN ONE CLOCK PERIOD, THE DATA TRANSITION CAN BE PROGRAMMED TO 64 DIFFERENT LOCATIONS.

3. DCLK CAN BE INVERTED WITH RESPECT TO DOUT BY USING THE DCLKINV REGISTER.

Figure 20. Digital Output Phase Adjustment Using DOUTPHASEP Register

CLI

tCLIDLY

N

CCDIN

N + 1 N + 2 N + 3 N + 4 N + 5 N + 6 N + 7 N + 8 N + 9 N + 10 N + 11 N + 12 N + 13 N + 14 N + 15 N + 16 N + 17

SHD

(INTERNAL)

SAMPLE PIXEL N

ADC DOUT

(INTERNAL)

DCLK

DOUT

N – 17 N – 16 N – 15 N – 14 N – 13 N – 12 N – 11 N – 10 N – 9 N – 8 N – 7 N – 6 N – 5 N – 4 N – 3 N – 2 N – 1

N

N+1

tDOUTINH

PIPELINE LATENCY = 16 CYCLES

N – 17 N – 16 N – 15 N – 14 N – 13 N – 12 N – 11 N – 10 N – 9 N – 8 N – 7 N – 6 N – 5 N – 4 N – 3 N – 2 N – 1

N

N+1

NOTES

1. TIMING VALUES SHOWN ARE SHDLOC = 0, WITH DCLKMODE = 0.

2. HIGHER VALUES OF SHD AND/OR DOUT PHASE SHIFTS DOUT TRANSITION TO THE RIGHT, WITH RESPECT TO CLI LOCATION.

3. RECOMMENDED VALUE FOR DOUT PHASE IS TO USE SHPLOC OR UP TO 15 EDGES FOLLOWING SHPLOC.

Figure 21. Digital Data Output Pipeline Delay

Rev. C | Page 18 of 92