ADV7152LS220 データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

ADV7152LS220 Datasheet PDF : 32 Pages

| |||

ADV7152

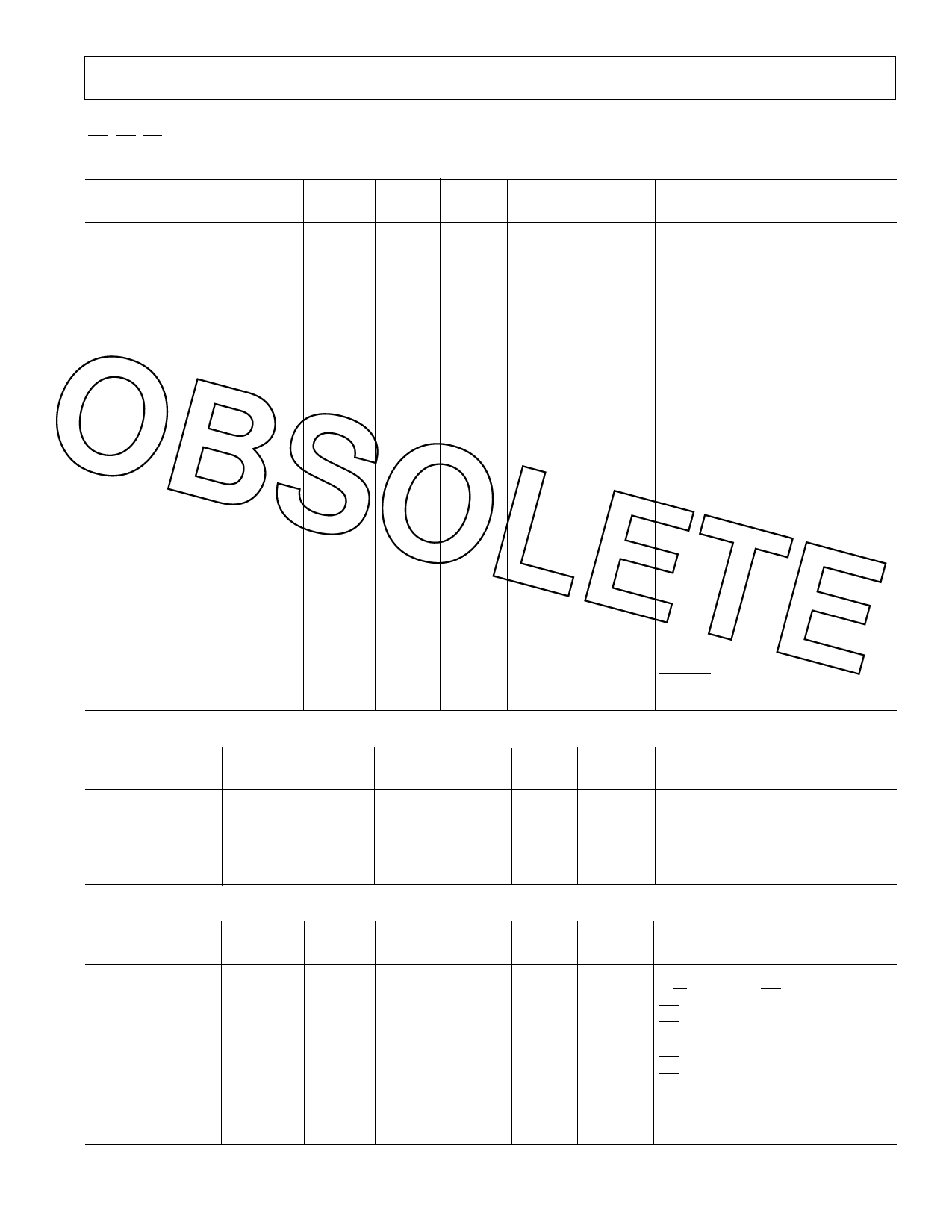

TIMING CHARACTERISTICS1

(VAA2 = +5 V; VREF = +1.235 V; RSET = 280 ⍀. IOR, IOG, IOB (RL = 37.5 ⍀, CL = 10 pF);

IOR, IOG, I0B = GND. All specifications TMIN to TMAX3 unless otherwise noted.)

CLOCK CONTROL AND PIXEL PORT4

Parameter

220 MHz 170 MHz 135 MHz 110 MHz 85 MHz

Version Version Version Version Version Units

Conditions/Comments

fCLOCK

220

170

135

110

85

MHz max Pixel CLOCK Rate

t1

4.55

5.88

7.4

9.1

11.77 ns min Pixel CLOCK Cycle Time

t2

2

2.5

3

4

4

ns min Pixel CLOCK High Time

t3

2

2.5

3.2

4

4

ns min Pixel CLOCK Low Time

t4

10

10

10

10

10

ns max Pixel CLOCK to LOADOUT Delay

fLOADIN

LOADIN Clocking Rate

OBSOLETE 1:1Multiplexing 110

2:1 Multiplexing 110

t5

1:1 Multiplexing 9.1

2:1 Multiplexing 9.1

t6

1:1 Multiplexing 4

2:1 Multiplexing 4

t7

1:1 Multiplexing 4

2:1 Multiplexing 4

t8

0

t9

5

t10

0

τ–t115

τ–5

tPD6

1:1 Multiplexing 5

2:1 Multiplexing 6

110

110

85

67.5

9.1

9.1

11.76 14.8

4

4

5

6

4

4

5

6

0

0

5

5

0

0

τ–5

τ–5

5

5

6

6

110

55

9.1

18.18

4

8

4

8

0

5

0

τ–5

5

6

85

42.5

11.76

23.53

4

9

4

9

0

5

0

τ–5

5

6

MHz max

MHz max

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns max

CLOCKs

CLOCKs

LOADIN Cycle Time

LOADIN High Time

LOADIN Low Time

Pixel Data Setup Time

Pixel Data Hold Time

LOADOUT to LOADIN Delay

LOADOUT to LOADIN Delay

Pipeline Delay

(1 × CLOCK = t1)

t12

10

10

10

10

10

ns max Pixel CLOCK to PRGCKOUT Delay

t13

5

5

5

5

5

ns max SCKIN to SCKOUT Delay

t14

5

5

5

5

5

ns min BLANK to SCKIN Setup Time

t15

1

1

1

1

1

ns min BLANK to SCKIN Hold Time

ANALOG OUTPUTS7

Parameter

220 MHz 170 MHz 135 MHz 110 MHz 85 MHz

Version Version Version Version Version Units

t16

15

15

15

15

15

ns typ

t17

1

1

1

1

1

ns typ

t18

15

15

15

15

15

ns typ

tSK

2

2

2

2

2

ns max

0

0

0

0

0

ns typ

Conditions/Comments

Analog Output Delay

Analog Output Rise/Fall Time

Analog Output Transition Time

Analog Output Skew (IOR, IOG, IOB)

MPU PORTS8, 9

Parameter

t19

t20

t21

t22

t238

t249

t259

t26

t27

220 MHz 170 MHz 135 MHz 110 MHz 85 MHz

Version Version Version Version Version Units

3

3

3

3

3

ns min

10

10

10

10

10

ns min

45

45

45

45

45

ns min

25

25

25

25

25

ns min

5

5

5

5

5

ns min

45

45

45

45

45

ns max

20

20

20

20

20

ns max

5

5

5

5

5

ns min

20

20

20

20

20

ns min

5

5

5

5

5

ns min

Conditions/Comments

R/W, C0, C1 to CE Setup Time

R/W, C0, C1 to CE Hold Time

CE Low Time

CE High Time

CE Asserted to Databus Driven

CE Asserted to Data Valid

CE Disabled to Databus Three-Stated

Write Data (D0–D9) Setup Time

Write Data (D0–D9) Hold Time

REV. B

–3–