AM24LC04 データシートの表示(PDF) - Anachip Corporation

部品番号

コンポーネント説明

メーカー

AM24LC04 Datasheet PDF : 12 Pages

| |||

2-Wire Serial 4K-Bit (512 x 8) CMOS Electrically Erasable PROM

ATC

AM24LC04

Pin Descriptions

Serial Clock (SCL)

The SCL input is used to clock all data into and out

of the device.

Serial Data (SDA)

SDA is a bidirection pin used to transfer data into

and out of the device.

It is an open drain output and may be wire-ORed

with any number of open drain or open collector

outputs. Thus, the SDA bus requires a pull-up

resistor to Vcc (typical 4.7KΩ for 100KHz)

Device Address Inputs (A0, A1, A2)

The following table (Table A) shows the active pins

across the AM24LCXX device family.

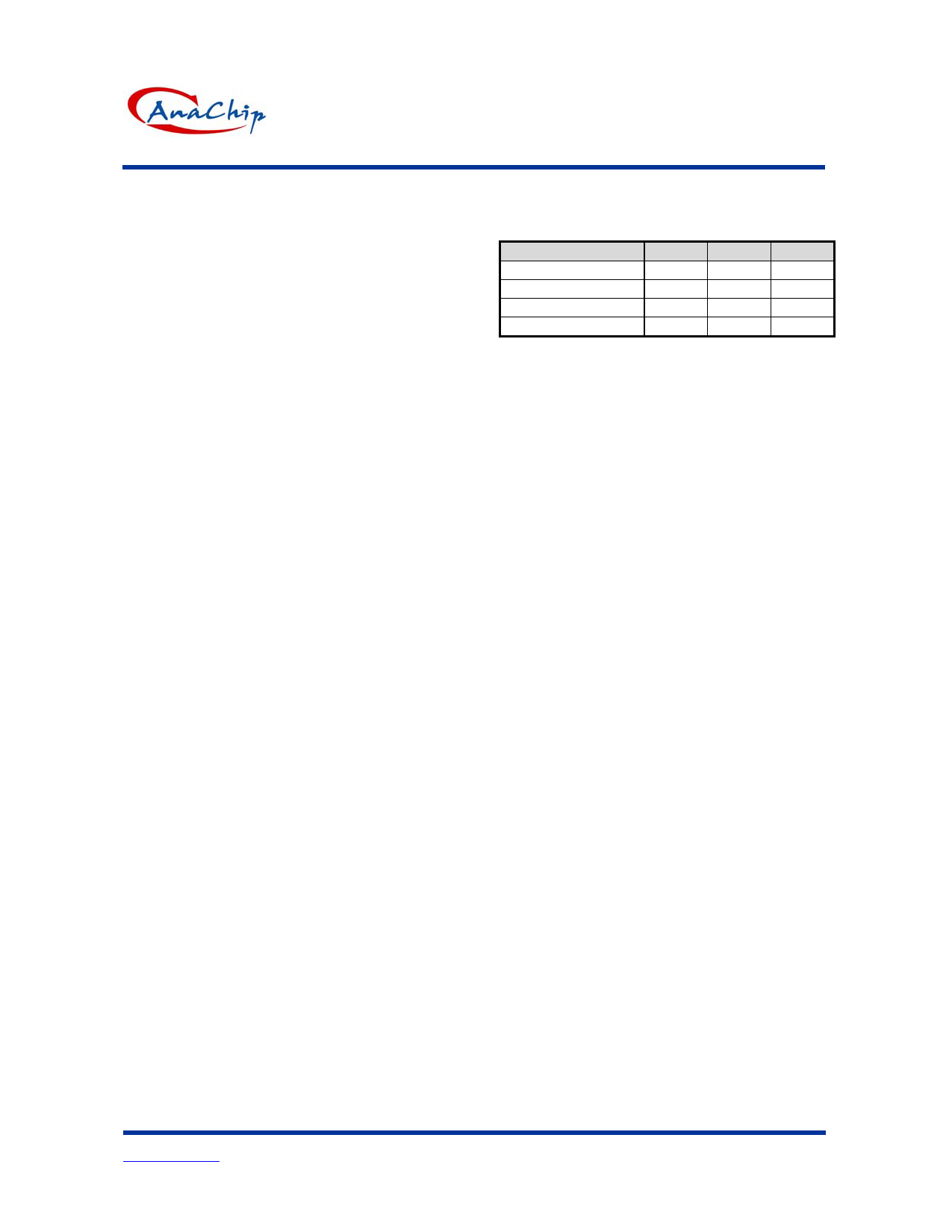

Table A

Device

A0

A1

A2

AM24LC02

ADR ADR ADR

AM24LC04

XP

ADR ADR

AM24LC08

XP

XP

ADR

AM24LC16

XP

XP

XP

ADR indicates the device address pin.

XP indicates that device address pin don’t care but

refers to an internal PAGE BLOCK memory

segment.

Write Protection (WP)

If WP is connected to Vcc, PROGRAM operation

onto the whole memory will not be executed. READ

operations are possible. If WP is connected to Vss,

normal memory operation is enabled, READ/WRITE

over the entire memory is possible.

Functional Description

Applications

ATC’s electrically erasable programmable read only

memories (EEPROMs) write protect function, two

write modes, three read modes, and a wide variety

of memory size. Typical applications for the I2C bus

and AM24LCXX memories are included in

SANs(small-area-networks), stereos, televisions,

automobiles and other scaled-down systems that

don't require tremendous speeds but instead cost

efficiency and design simplicity.

Clock and Data Conventions

Data states on the SDA line can change only during

SCL LOW. SDA state changes during SCL HIGH

are reserved for indicating start and stop conditions.

(Shown in Figures 1 and 2)

Start Condition

A HIGH to LOW transition of the SDA line while the

clock (SCL) is HIGH determines a START condition.

All commands must be preceded by a START

condition. (Shown in Figure 2)

Endurance and Data Retention

The AM24LC04 is designed for applications

requiring up to 1M programming cycles (BYTE

WRITE and PAGE WRITE). It provides 40 years of

secure data retention without power.

Stop Condition

A LOW to HIGH transition of the SDA line while the

clock (SCL) is HIGH determines a STOP condition.

All operations must be ended with a STOP condition.

(Shown in Figure 2)

Device Operation

The AM24LC04 support a bi-directional bus oriented

protocol. The protocol defines any device that sends

data onto the bus as a transmitter and the receiving

device as the receiver. The device controlling the

transfer is the master and the device that is

controlled is the slave. The master will always

initiate data transfers and provide the clock for both

transmit and receive operations. Therefore, the

AM24LC04 is considered a slave in all applications.

Anachip Corp.

www.anachip.com.tw

Rev. A2 Oct 20, 2003

4/12