AT25640A-10PI-2.7 データシートの表示(PDF) - Atmel Corporation

部品番号

コンポーネント説明

メーカー

AT25640A-10PI-2.7

AT25640A-10PI-2.7 Datasheet PDF : 19 Pages

| |||

Functional

Description

AT25080A/160A/320A/640A

The AT25080A/160A/320A/640A is designed to interface directly with the synchronous serial

peripheral interface (SPI) of the 6805 and 68HC11 series of microcontrollers.

The AT25080A/160A/320A/640A utilizes an 8-bit instruction register. The list of instructions

and their operation codes are contained in Table 5. All instructions, addresses, and data are

transferred with the MSB first and start with a high-to-low CS transition.

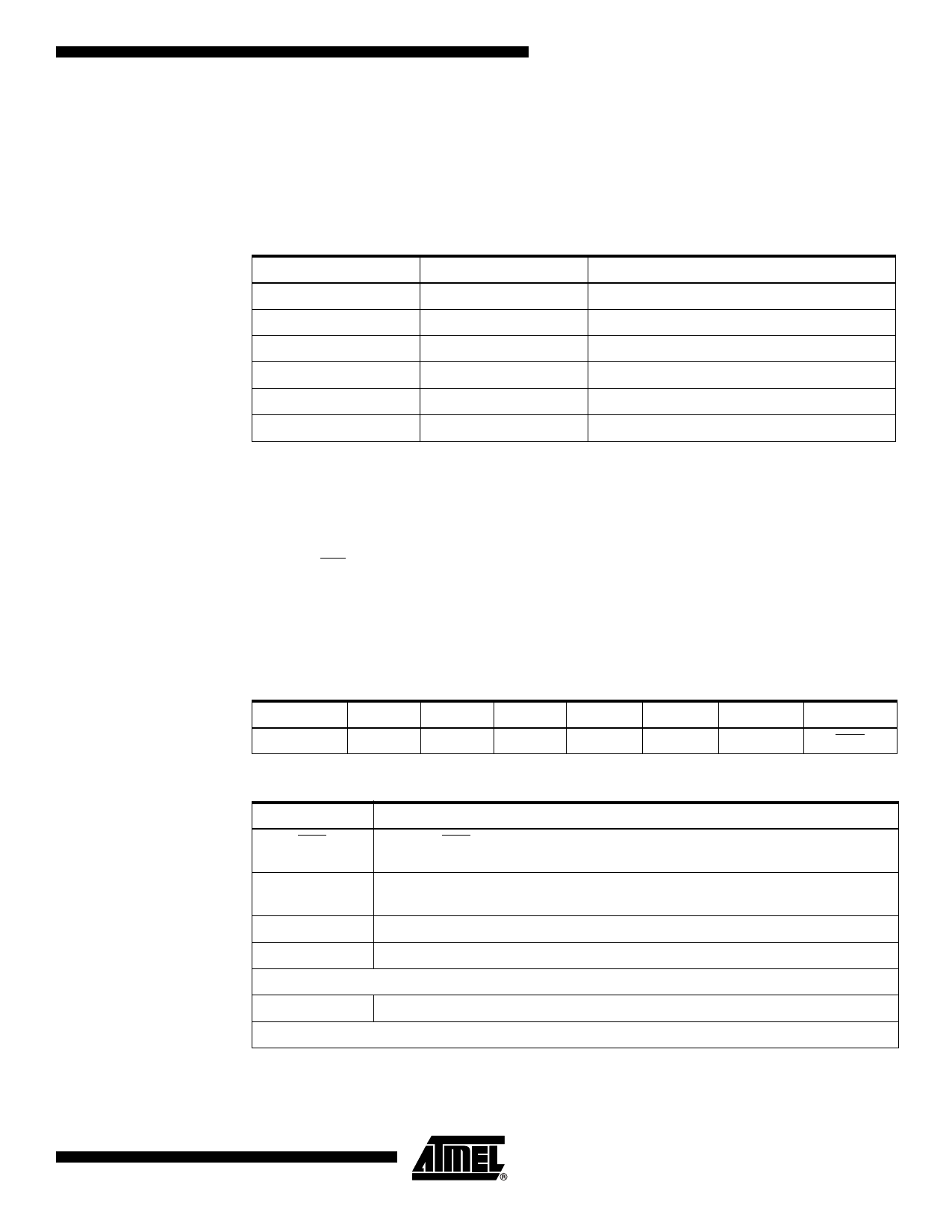

Table 5. Instruction Set for the AT25080A/160A/320A/640A

Instruction Name

Instruction Format

Operation

WREN

0000 X110

Set Write Enable Latch

WRDI

0000 X100

Reset Write Enable Latch

RDSR

0000 X101

Read Status Register

WRSR

0000 X001

Write Status Register

READ

0000 X011

Read Data from Memory Array

WRITE

0000 X010

Write Data to Memory Array

WRITE ENABLE (WREN): The device will power-up in the write disable state when VCC is

applied. All programming instructions must therefore be preceded by a Write Enable

instruction.

WRITE DISABLE (WRDI): To protect the device against inadvertent writes, the Write Disable

instruction disables all programming modes. The WRDI instruction is independent of the sta-

tus of the WP pin.

READ STATUS REGISTER (RDSR): The Read Status Register instruction provides access to

the status register. The READY/BUSY and Write Enable status of the device can be deter-

mined by the RDSR instruction. Similarly, the Block Write Protection bits indicate the extent of

protection employed. These bits are set by using the WRSR instruction.

Table 6. Status Register Format

Bit 7

Bit 6

Bit 5

WPEN

X

X

Bit 4

X

Bit 3

BP1

Bit 2

BP0

Bit 1

WEN

Bit 0

RDY

Table 7. Read Status Register Bit Definition

Bit

Definition

Bit 0 (RDY)

Bit 0 = 0 (RDY) indicates the device is ready. Bit 0 = 1 indicates the write cycle is in

progress.

Bit 1 (WEN)

Bit 1= 0 indicates the device is not write-enabled. Bit 1 = 1 indicates the device is

write-enabled.

Bit 2 (BP0)

See Table 8 on page 8.

Bit 3 (BP1)

See Table 8 on page 8.

Bits 4–6 are “0”s when device is not in an internal write cycle.

Bit 7 (WPEN)

See Table 9 on page 8.

Bits 0–7 are “1”s during an internal write cycle.

7

3401C–SEEPR–8/04