AZ100LVEL16VV(2012) データシートの表示(PDF) - Arizona Microtek, Inc

部品番号

コンポーネント説明

メーカー

AZ100LVEL16VV

(Rev.:2012)

(Rev.:2012)

AZ100LVEL16VV Datasheet PDF : 9 Pages

| |||

Arizona Microtek, Inc.

ENGINEERING NOTES

AZ100LVEL16VV

Dual Frequency PECL/ECL Oscillator

Gain Stage & Buffer with Enable

The data inputs are selected with the select pin (SEL). When SEL is LOW or open (NC) data from the D0/D¯¯0 is selected.

When SEL is HIGH data from the D1/D¯¯1 is selected. See Table 2 for data selection.

The enable pin (EN) works with either data input pair. When EN is HIGH or open (NC), input data is passed to both sets

of outputs. When EN is LOW, the QHG/Q¯ HG outputs will be forced LOW/HIGH respectively, while input data will

continue to be passed to the Q/Q¯ outputs. The EN and SEL inputs can be driven with an ECL/PECL signal or a full supply

swing CMOS type logic signal. See table 2 for enable operation.

Internal Input biasing is accomplished with a VBB and separate 470Ω bias resistors connecting each data input to VBB . The

VBB pin supports 1.5mA sink/source current and should be bypassed to ground with a 0.01µF capacitor.

Each Q/Q¯ output has a 4 mA on-chip pull-down current source. External resistors may also be used to increase pull-down

current of the Q/Q¯ to a maximum of 25mA each (includes a 4 mA on-chip current source).

NOTE: Specifications in the ECL/PECL tables are valid when thermal equilibrium is established.

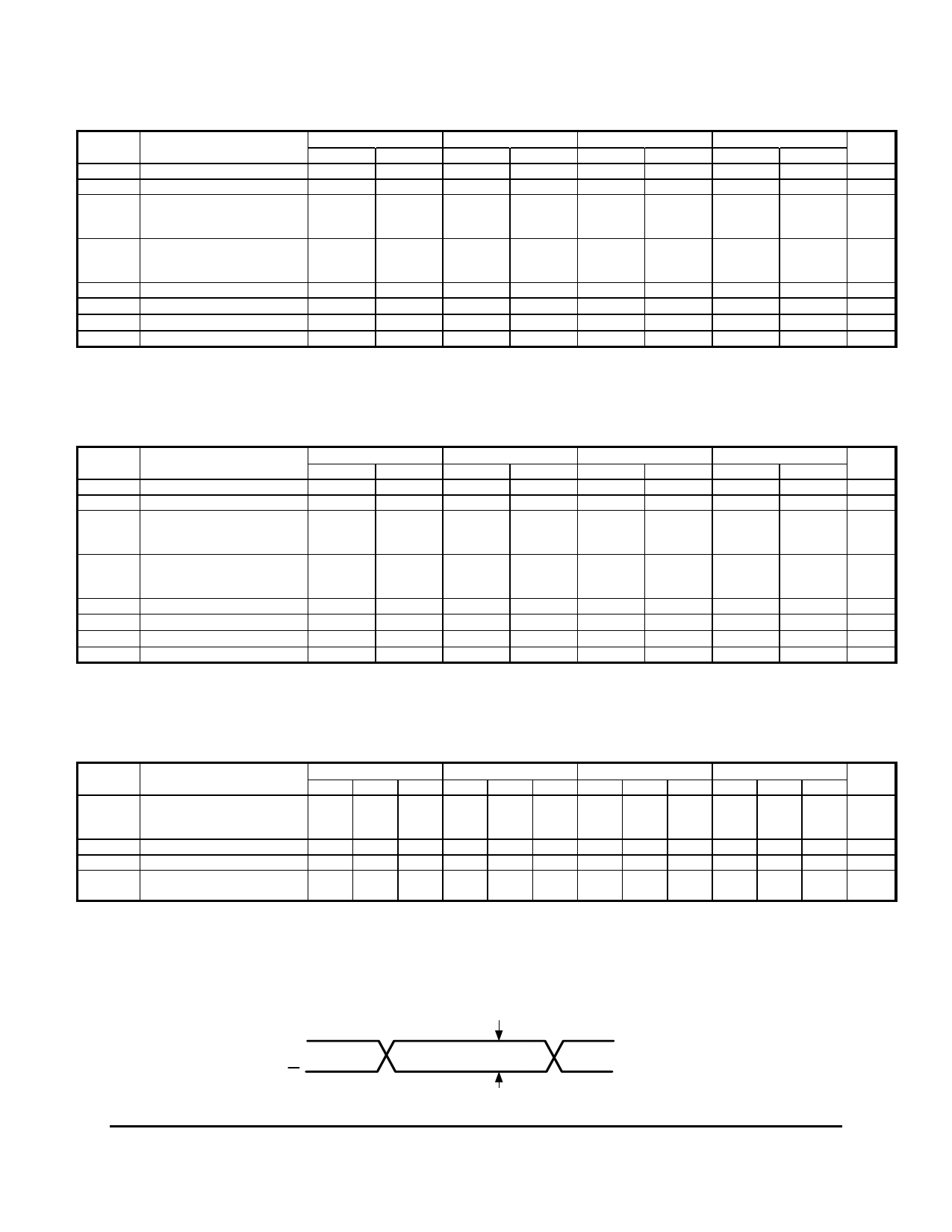

Table 2 - Truth Table

EN

High/Open

High/Open

Low

Low

CS-SEL

Low/Open

High

Low/Open

High

Q

D0/D¯¯0

D1/D¯¯1

D0/D¯¯0

D1/D¯¯1

Q¯

D0/D¯¯0

D1/D¯¯1

D0/D¯¯0

D1/D¯¯1

QHG

D0/D¯¯0

D1/D¯¯1

Low

Low

Q¯ HG

D0/D¯¯0

D1/D¯¯1

High

High

D0

D1

EN

SEL

Q

Q

QHG

QHG

www.azmicrotek.com

+1-480-962-5881

Request a Sample

Figure 2 - Timing Diagram

3

May 2012, Rev 2.0