BCM5632E データシートの表示(PDF) - Broadcom Corporation

部品番号

コンポーネント説明

メーカー

BCM5632E Datasheet PDF : 2 Pages

| |||

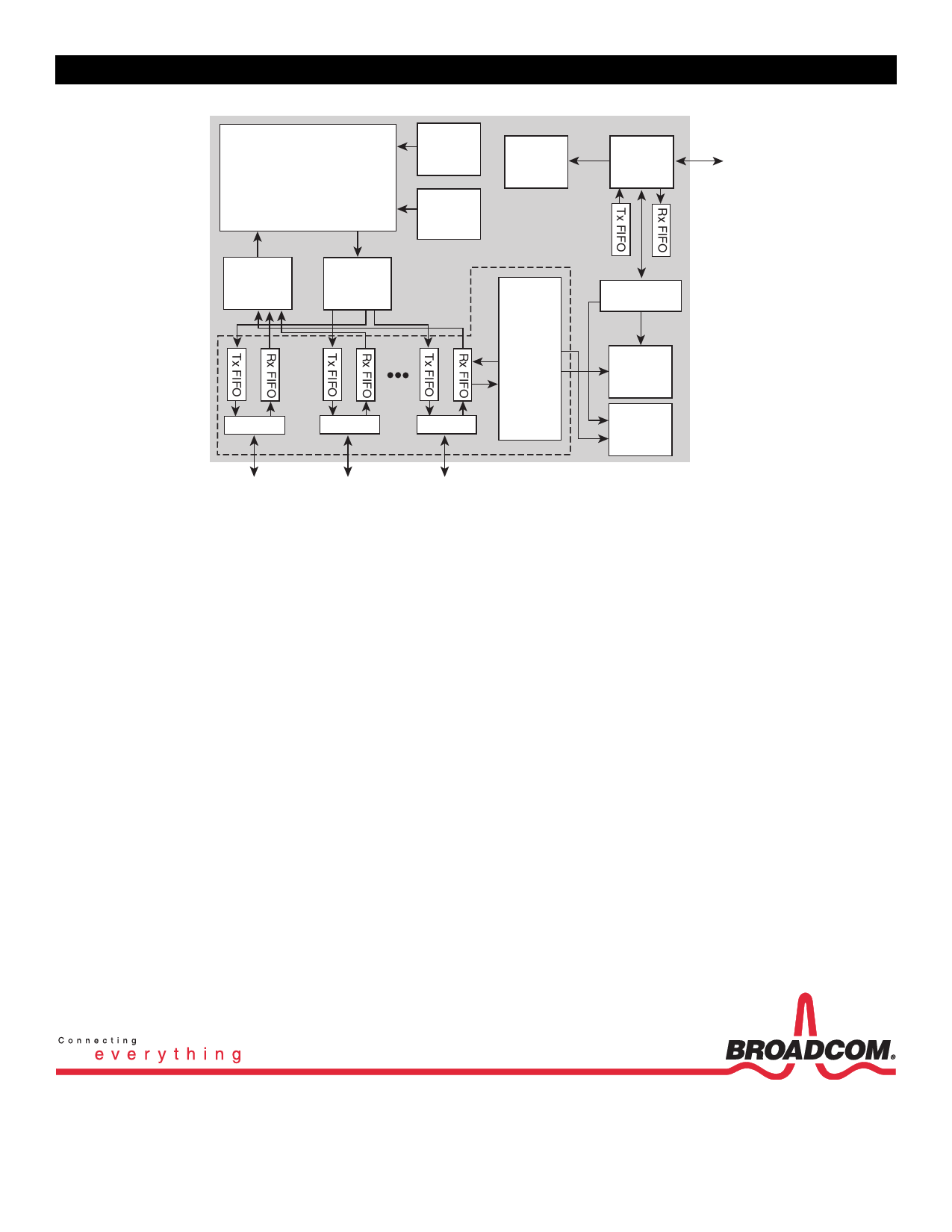

OVERVIEW

Shared Buffer

Output

Queueing

Buffer

Manager

MIB

Counters

PCI

Interface

To CPU

Serial

to

Parallel

Parallel

to

Serial

Port

Manager

Table

Maintenance

L2 MAC

Table

10 G MAC

G MAC

G MAC

VLAN

Table

10 G-Port

G-Port

G-Port

The BCM5632E switching processor chip supports 12 Gigabit ports and

one 10-Gigabit uplink with all ports in wirespeed operation. The

BCM5632E is ideal for applications such as multi-Gigabit port switches

or aggregating multiple-Gigabit ports to a 10-Gigabit backplane.

For Gigabit ports, the BCM5632E supports PCS (802.3z, 1000BASE-X)

or GMII (802.3ab, 1000BASE-T) interfaces with full-duplex operation

at Gigabit speed, and full- or half-duplex operation at 10/100 Mbps speed

(using 1000BASE-T). For the uplink port, the BCM5632E supports

XGMII.

The BCM5632E supports 802.1Q VLAN tagging as an option (Qon).

The BCM5632E supports 802.1v VLAN Classification by Protocol.

There are four user-programmable protocols that can be set up per port

by the VLAN Classification EtherType and the VLAN Priority/TAG

registers.

The BCM5632E supports 32K internal MAC addresses which are shared

by all ports. Multicast MAC addresses including IP multicast can also be

stored and searched.

The BCM5632E also supports 4K VLAN addresses with the 802.1s

Multiple Spanning Tree option, and flexible and programmable ingress

and egress checking rules for VLAN processing.

The BCM5632E also supports 802.3ad port aggregation. The 12-Gigabit

ports can form up to six trunks, with a maximum of twelve ports in a

trunk. The distribution algorithm is user-selectable. The Link

Aggregation Control Protocol (LACP) frames are handled by the

accompanying CPU and the marker protocol is handled in hardware.

The BCM5632E can be initialized and configured by an EEPROM or a

CPU, which is also responsible for search table updates and management

functions. The CPU is a separate port to the device, containing its own

Tx FIFO and Rx FIFO. The device implements a 32-bit, 33-MHz

Peripheral Component Interconnect (PCI) for flexible CPU selection and

interface.

Other features include frame trapping and forwarding to the CPU, port

monitoring, and broadcast storm control to reduce broadcast traffic

through the switch. The BCM5632E also offers a flexible multiplexer

mode in which the L2 switching functionality can be turned on and off

on a per-port basis.

Broadcom®, the pulse logo, and Connecting everything® are trademarks of Broadcom Corporation and/

or its subsidiaries in the United States and certain other countries. All other trademarks mentioned are the

property of their respective owners.

®

BROADCOM CORPORATION

16215 Alton Parkway, P.O. Box 57013

Irvine, California 92619-7013

© 2004 by BROADCOM CORPORATION. All rights reserved.

5632E-PB01-R 07/08/04

Phone: 949-450-8700

Fax: 949-450-8710

E-mail: info@broadcom.com

Web: www.broadcom.com