CAT25C01LI データシートの表示(PDF) - Catalyst Semiconductor => Onsemi

部品番号

コンポーネント説明

メーカー

CAT25C01LI Datasheet PDF : 15 Pages

| |||

CAT25C01, CAT25C02, CAT25C04

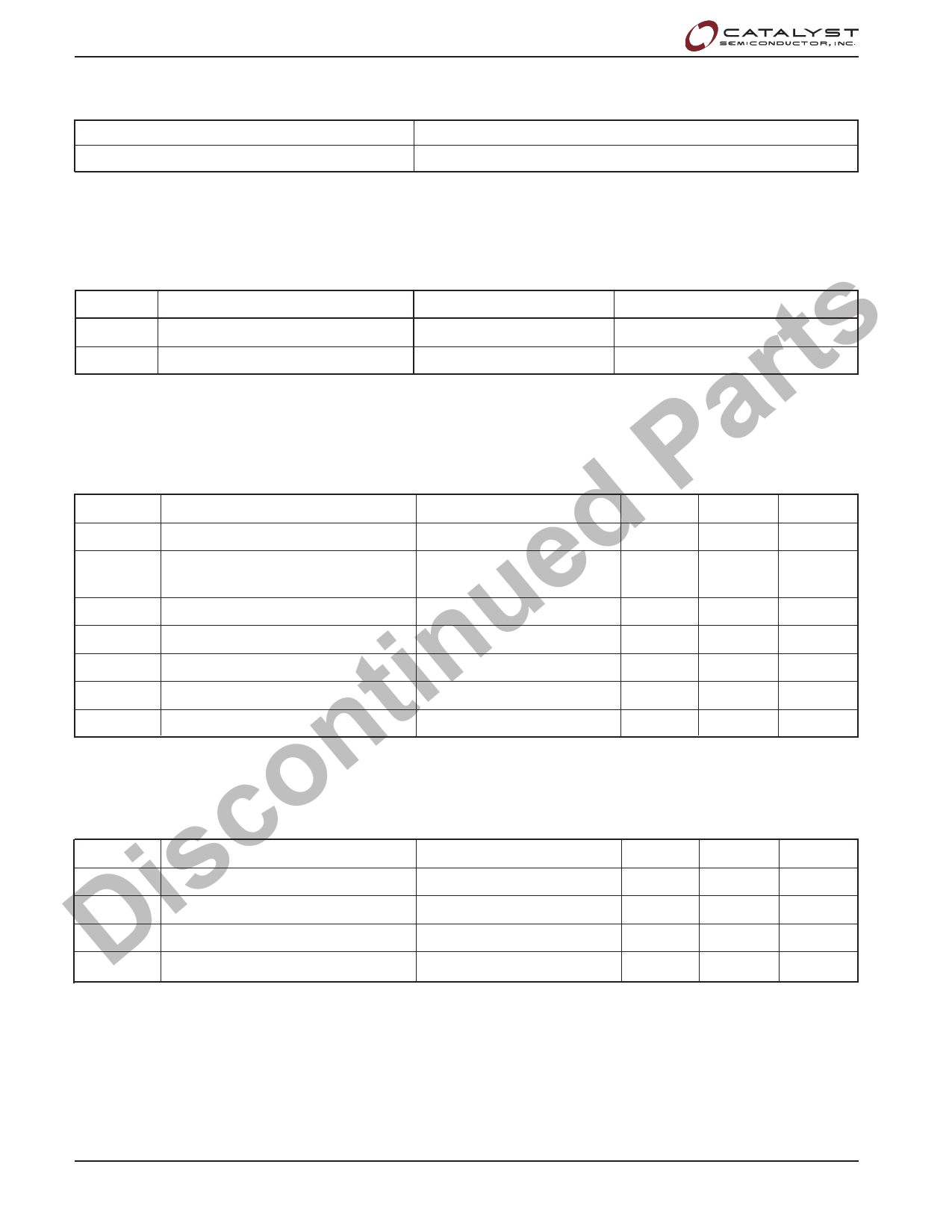

ABSOLUTE MAXIMUM RATINGS*

Storage Temperature

Voltage on Any Pin with Respect to Ground(1)

-65°C to +150°C

-0.5 V to +6.5 V

* Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only,

and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification

is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

RELIABILITY CHARACTERISTICS(2)

Symbol Parameter

NEND(*)

ts TDR

Endurance

Data Retention

(*) Page Mode, VCC = 5 V, 25°C

Min

1,000,000

100

Units

Program/ Erase Cycles

Years

ar D.C. OPERATING CHARACTERISTICS

VCC = 1.8 V to 5.5 V, TA = -40°C to 85°C, unless otherwise specified.

P Symbol Parameter

Test Conditions

Min

Max

ICC

d ISB

e IL

u VIL

VIH

tin VOL1

VOL2

Supply Current

Standby Current

I/O Pin Leakage

Input Low Voltage

Input High Voltage

Output Low Voltage

Output Low Voltage

Read or Write at 5 MHz

1

All I/O Pins at GND or VCC,

2

CS = VCC

Pin at GND or VCC

2

-0.5 VCC x 0.3

VCC x 0.7 VCC + 0.5

VCC > 2.5 V, IOL = 3.0 mA

0.4

VCC > 1.8 V, IOL = 1.0 mA

0.2

Units

mA

µA

µA

V

V

V

V

n PIN IMPEDANCE CHARACTERISTICS

o TA = 25°C, f = 1 MHz, VCC = 5 V

c Symbol

CIN(2)

is CIN(2)

DZWPL

Parameter

SDA I/O Pin Capacitance

Input Capacitance (other pins)

WP Input Low Impedance

Conditions

VIN = 0 V

VIN = 0 V

VIN < 0.5 V

Min

Max

Units

8

pF

6

pF

5

70

kΩ

ILWPH

WP Input High Leakage

VIN > VCC x 0.7

2

µA

Note:

(1) The DC input voltage on any pin should not be lower than -0.5 V or higher than VCC + 0.5 V. During transitions, the voltage on any pin

may undershoot to no less than -1.5 V or overshoot to no more than VCC + 1.5 V, for periods of less than 20 ns.

(2) These parameters are tested initially and after a design or process change that affects the parameter according to appropriate AEC-Q100

and JEDEC test methods.

Doc. No. 1105, Rev. B

2

© 2005 by Catalyst Semiconductor, Inc.

Characteristics subject to change without notice