CAT25C03GL データシートの表示(PDF) - Catalyst Semiconductor => Onsemi

部品番号

コンポーネント説明

メーカー

CAT25C03GL Datasheet PDF : 12 Pages

| |||

CAT25C11/03/05/09/17

SPI modes (0,0 & 1,1).

and forces the devices into a Standby Mode (unless an

internal write operation is underway) The CAT25C11/03/

SCK: Serial Clock

05/09/17 draws ZERO current in the Standby mode. A

SCK is the serial clock pin. This pin is used to synchronize high to low transition on CS is required prior to any

the communication between the microcontroller and the sequence being initiated. A low to high transition on CS

25C11/03/05/09/17. Opcodes, byte addresses, or data after a valid write sequence is what initiates an internal

present on the SI pin are latched on the rising edge of the write cycle.

SCK. Data on the SO pin is updated on the falling edge of

the SCK for SPI modes (0,0 & 1,1).

WP: Write Protect

WP is the Write Protect pin. The Write Protect pin will allow

CS: Chip Select

normal read/write operations when held high. When WP is

CS is the Chip select pin. CS low enables the CAT25C11/

03/05/09/17 and CS high disables the CAT25C11/03/05/

09/17. CS high takes the SO output pin to high impedance

BYTE ADDRESS

tied low and the WPEN bit in the status register is set to "1",

all write operations to the status register are inhibited. WP

going low while CS is still low will interrupt a write to the

status register. If the internal write cycle as already been

initiated, WP going low will have no effect on any write

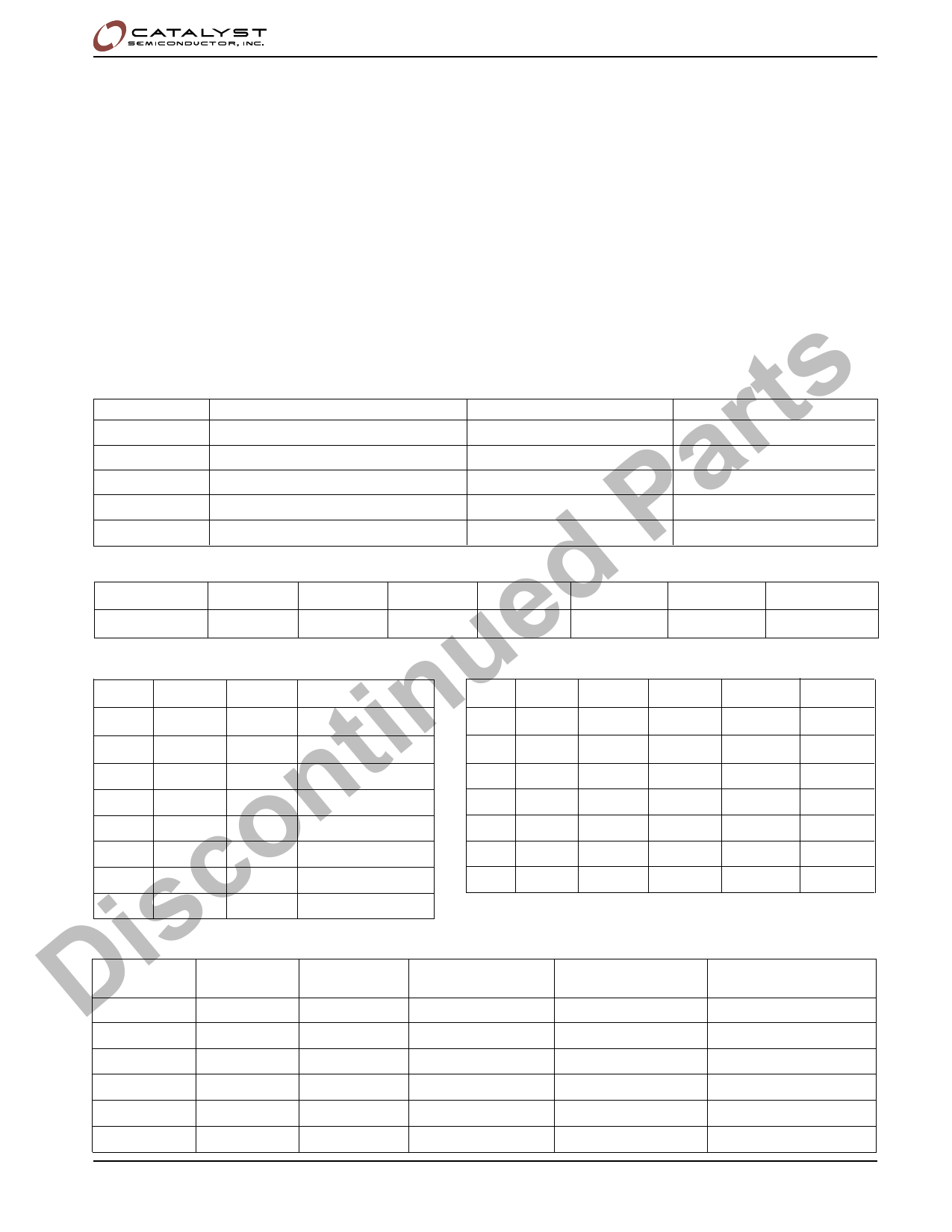

ts Device

Address Significant Bits

Address Don't Care Bits # Address Clock Pulse

CAT25C11

A6 - A0

A7

8

r CAT25C03

A7 - A0

—

8

CAT25C05 A7 - A0 (A8 = X bit from Opcode)

—

8

a CAT25C09

A9 - A0

A15 - A10

16

CAT25C17

A10 - A0

A15 - A11

16

P STATUS REGISTER

7

6

d WPEN

1

5

4

3

2

1

0

1

BP2

BP1

BP0

WEL

RDY

e MEMORY PROTECTION

u BP2 BP1 BP0

0

0

0

Non-Protection

tin 0

0

1

Q1 Protected

0

1

0

Q2 Protected

0

1

1

Q3 Protected

n 1

0

0

Q4 Protected

1

0

1

H1 Protected

o 1

1

0

P0 Protected

c 1

1

1

Pn Protected

WRITE PROTECT ENABLE OPERATION

25C11 25C03 25C05 25C09 25C17

Q1 00-1F 00-3F 000-07F 000-0FF 000-1FF

Q2 20-3F 40-7F 080-0FF 100-1FF 200-3FF

Q3 40-5F 80-BF 100-17F 200-2FF 400-5FF

Q4 60-7F C0-FF 180-1FF 300-3FF 600-7FF

H1 00-3F 00-7F 000-0FF 000-1FF 000-3FF

P0 00-0F 00-0F 000-00F 000-01F 000-01F

Pn 70-7F F0-FF 1F0-1FF 3E0-3FF 7E0-7FF

is Protected

Unprotected

WPEN

WP

WEL

Blocks

Blocks

D0

X

0

Protected

Protected

Status

Register

Protected

0

X

1

Protected

Writable

Writable

1

Low

0

Protected

Protected

Protected

1

Low

1

Protected

Writable

Protected

X

High

0

Protected

Protected

Protected

X

High

1

Protected

Writable

Writable

© 2005 by Catalyst Semiconductor, Inc.

Characteristics subject to change without notice

5

Doc. No. 1017, Rev. L