CAT25C03GL データシートの表示(PDF) - Catalyst Semiconductor => Onsemi

部品番号

コンポーネント説明

メーカー

CAT25C03GL Datasheet PDF : 12 Pages

| |||

CAT25C11/03/05/09/17

enable latch will not have been properly set. Also, for a device. If the write operation is initiated immediately after

successful write operation the address of the memory the WREN instruction without CS being brought high,

location(s) to be programmed must be outside the pro- the data will not be written to the array because the write

tected address field.

up to 16 bytes of data to the CAT25C11/03/05 and 32

Byte Write

bytes of data for 25C09/17. After each byte of data

received, lower order address bits are internally

Once the device is in a Write Enable state, the user may

incremented by one; the high order bits of address

proceed with a write sequence by setting the CS low,

willremain constant.The only restriction is that the X

issuing a write instruction via the SI line, followed by the

(X=16 for 25C11/03/05 and X=32 for 25C09/17) bytes

16-bit address for 25C09/17. (only 10-bit addresses are

must reside on the same page. If the address counter

used for 25C09, 11-bit addresses are used for 25C17.

reaches the end of the page and clock continues, the

The rest of the bits are don't care bits) and 8-bit address

counter will “roll over” to the first address of the page and

for 25C11/03/05 (for the 25C05, bit 3 of the read data

instruction contains address A8). Programming will start

after the CS is brought high. Figure 6 illustrates byte write

sequence.

ts Page Write

The CAT25C11/03/05/09/17 features page write capa-

r bility. After the initial byte, the host may continue to write

after the WREN instruction to enable writes to thee

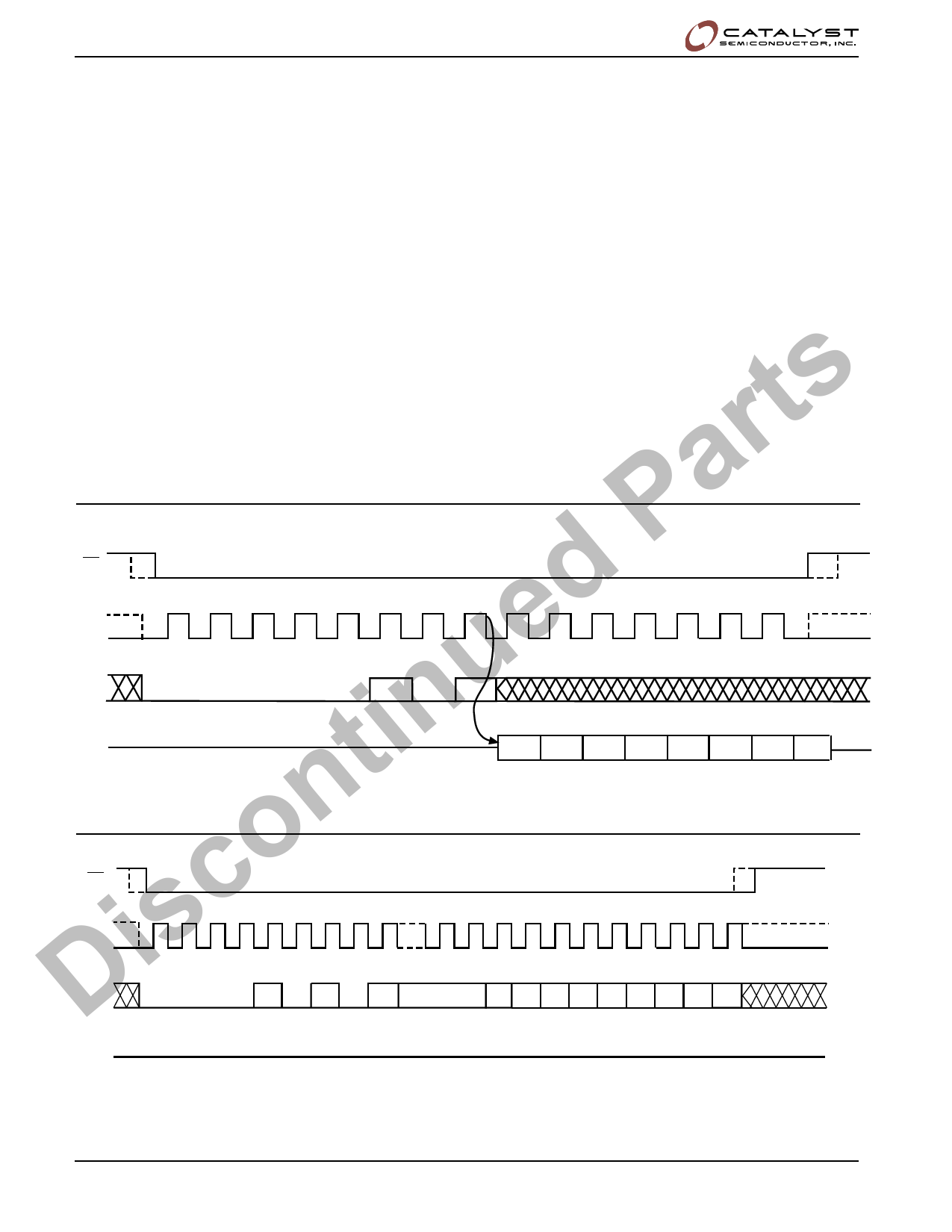

a Figure 5. RDSR Instruction Timing

overwrite any data that may have been written. The

CAT25C11/03/05/09/17 is automatically returned to the

write disable state at the completion of the write cycle.

Figure 8 illustrates the page write sequence.

To write to the status register, the WRSR instruction

should be sent. Only Bit 2, Bit 3, Bit 4 and Bit 7 of the

status register can be written using the write status

register instruction. Figure 7 illustrates the sequence of

writing to status register.

P CS

d SCK

0

1

2

3

4

5

6

7

8

9 10 11 12 13 14

e OPCODE

u SI

0

0

0

0

0

tin SO

HIGH IMPEDANCE

Note: Dashed Line= mode (1, 1) – – – –

1

0

1

DATA OUT

7

6

5

4

3

2

10

MSB

n Figure 6. Write Instruction Timing

o CS

c0 1 2 3 4 5 6 7 8

SK

*

*

21 22 23 24 25 26 27 28 29 30 31

is OPCODE

BYTE ADDRESS*

DATA IN

DSI

0 0 0 0 X* 0 1 0 AN

A0 D7 D6 D5 D4 D3 D2 D1 D0

SO

HIGH IMPEDANCE

*Please check the Byte Address Table

X = 0 for CAT25C11, CAT25C03, CAT25C09 and CAT25C17; X = A8 for CAT25C05

Note: Dashed Line= mode (1, 1) – – – –

Doc. No. 1017, Rev. L

8

© 2005 by Catalyst Semiconductor, Inc.

Characteristics subject to change without notice