CP8056 データシートの表示(PDF) - Unspecified

部品番号

コンポーネント説明

メーカー

CP8056 Datasheet PDF : 46 Pages

| |||

CHENGPIN

GENERAL DESCRIPTION

CP8056

The CP8056 series is a family of low-cost, high speed, high noise immunity, EPROM/ROM-based 8-bit CMOS

microcontrollers. It employs a RISC architecture with only 42 instructions. All instructions are single cycle except

for program branches which take two cycles. The easy to use and easy to remember instruction set reduces

development time significantly.

The CP8056 series consists of Power-on Reset (POR), Brown-out Reset (BOR), Power-up Reset Timer (PWRT),

Oscillator Start-up Timer(OST), Watchdog Timer, EPROM/ROM, SRAM, tri-state I/O port, I/O

pull-high/open-drain/pull-down control, Power saving SLEEP mode, real time programmable clock/counter,

Interrupt, Wake-up from SLEEP mode, and Code Protection for EPROM products. There are four oscillator

configurations to choose from, including the power-saving LP (Low Power) oscillator and cost saving RC oscillator.

The CP8056 address 1K×13 of program memory.

The CP8056 can directly or indirectly address its register files and data memory. All special function registers

including the program counter are mapped in the data memory.

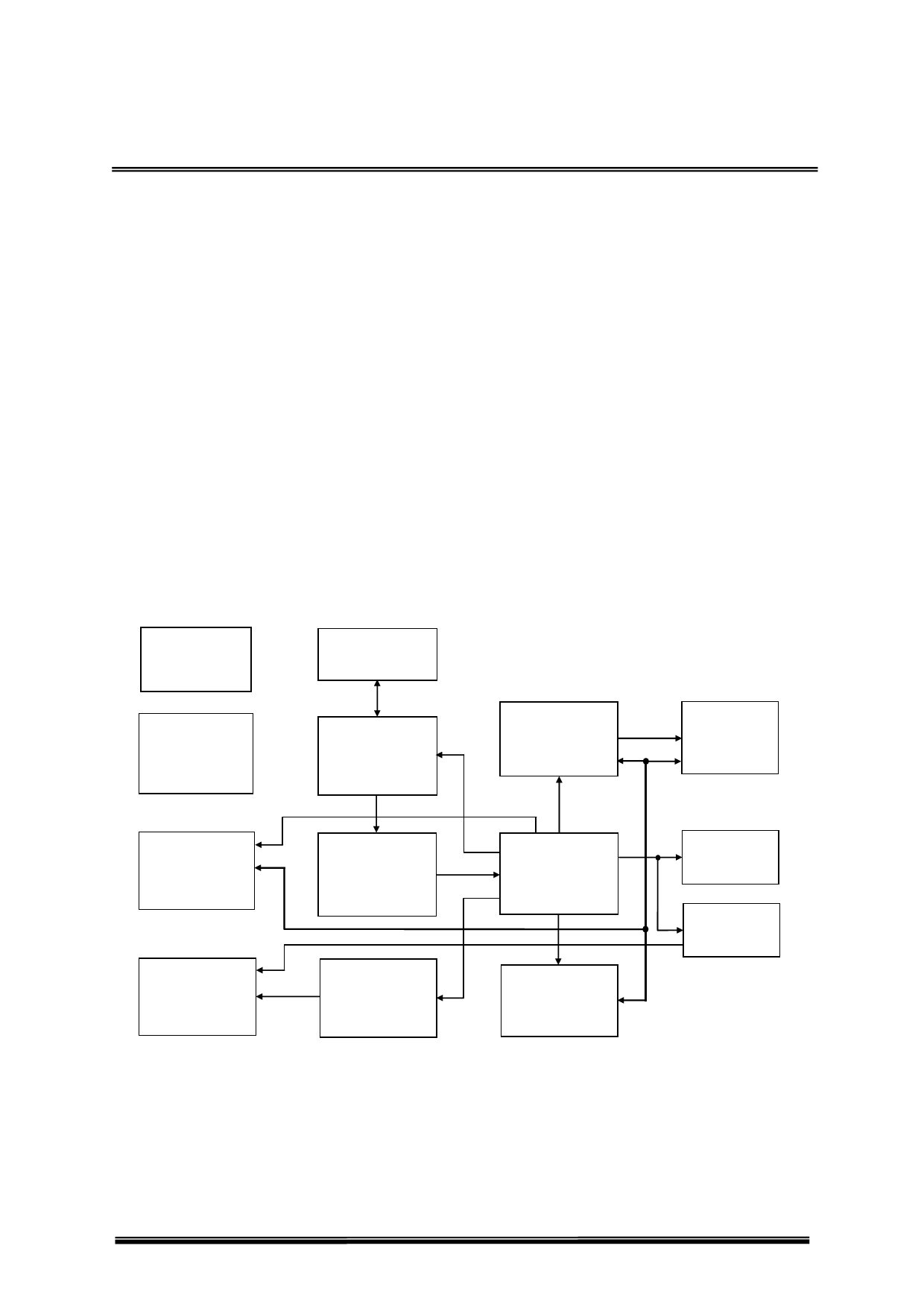

BLOCK DIAGRAM

Oscillator

Circuit

Watchdog

Timer

ALU

Interrupt

Control

5-level

STACK

Program

Counter

EPROM

/ ROM

Timer0

FSR

SRAM

Instruction

Decoder

Accumulator

PORTA

PORTB

P.2/CP8056