CS4614 データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

メーカー

CS4614 Datasheet PDF : 24 Pages

| |||

CS4614

CrystalClear™ SoundFusion™ PCI Audio Accelerator

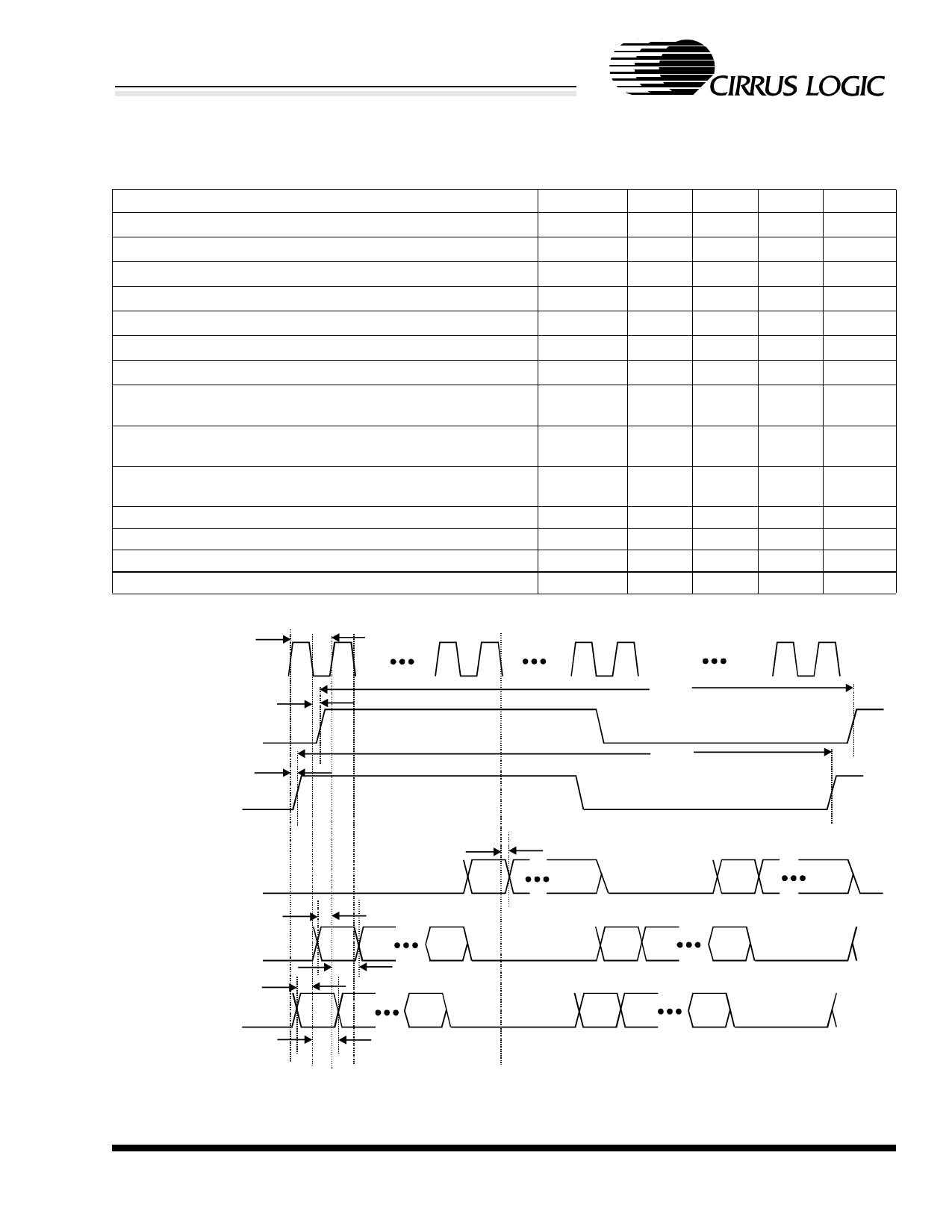

INDEPENDENT TIMING ENVIRONMENT (TA = 0 to 70° C; PCIVDD = CVDD = CRYVDD = 3.3 V;

VDD5REF = 5 V; VDD5REF = 5 V; PCIGND = CGND = CRYGND = 0 V; Logic 0 = 0V, Logic 1 = 3.3 V;

Timing reference levels = 1.4 V; XTALI = 12.288 MHz; unless otherwise noted)

Parameter

SCLK output cycle time

FSYNC output cycle time (@SCLK falling edge)

SCLK falling to FSYNC transition

LRCLK output cycle time (@ SCLK rising edge)

SCLK rising to LRCLK transition

SCLK falling to SDOUT/SDO2/SDO3 valid

SDIN/SDIN2 valid to SCLK rising (SI1F2-0: 010, SI2F1-0: 00)

SDIN/SDIN2 hold after SCLK rising

(SI1F2-0: 010, SI2F1-0: 00)

SDIN/SDIN2 valid to SCLK falling

(SI1F2-0: 011, SI2F1-0: 01)

SDIN/SDIN2 hold after SCLK falling

(SI1F2-0: 011, SI2F1-0: 01)

XTAL frequency

XTALI high time

XTALI low time

MCLK output frequency

(Note 4)

(Note 4)

(Note 4)

Symbol

tsclk

tfsync

tpd7

tlrclk

tpd8

tpd9

ts6

th6

ts7

th7

Min Typ Max

312

326

-

20000 20833

-

-45

2

45

20000 20833

-

-45

2

45

-

2

45

30

-

-

30

-

-

30

-

-

30

-

-

12.287

35

35

12.287

12.288

-

-

12.288

12.289

-

-

12.289

Units

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

MHz

ns

ns

MHz

tsclk

SCLK

tpd7

FSYNC

t pd8

LRCLK

t fsync

t lrclk

SDOUT/SD02/SD03

tpd9

15

0

15

0

SDIN/SDIN2

ts7

ts6

17 16

0

t h6

17 16

0

SDIN/SDIN2

19 18

0

th7

19 18

0

Figure 4. Independent Timing Configuration

DS292PP3

CIRRUS LOGIC PRELIMINARY PRODUCT BULLETIN JUNE 30, 5:03 PM

7