CS61577-IL1Z データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

メーカー

CS61577-IL1Z Datasheet PDF : 30 Pages

| |||

CS61577

#3

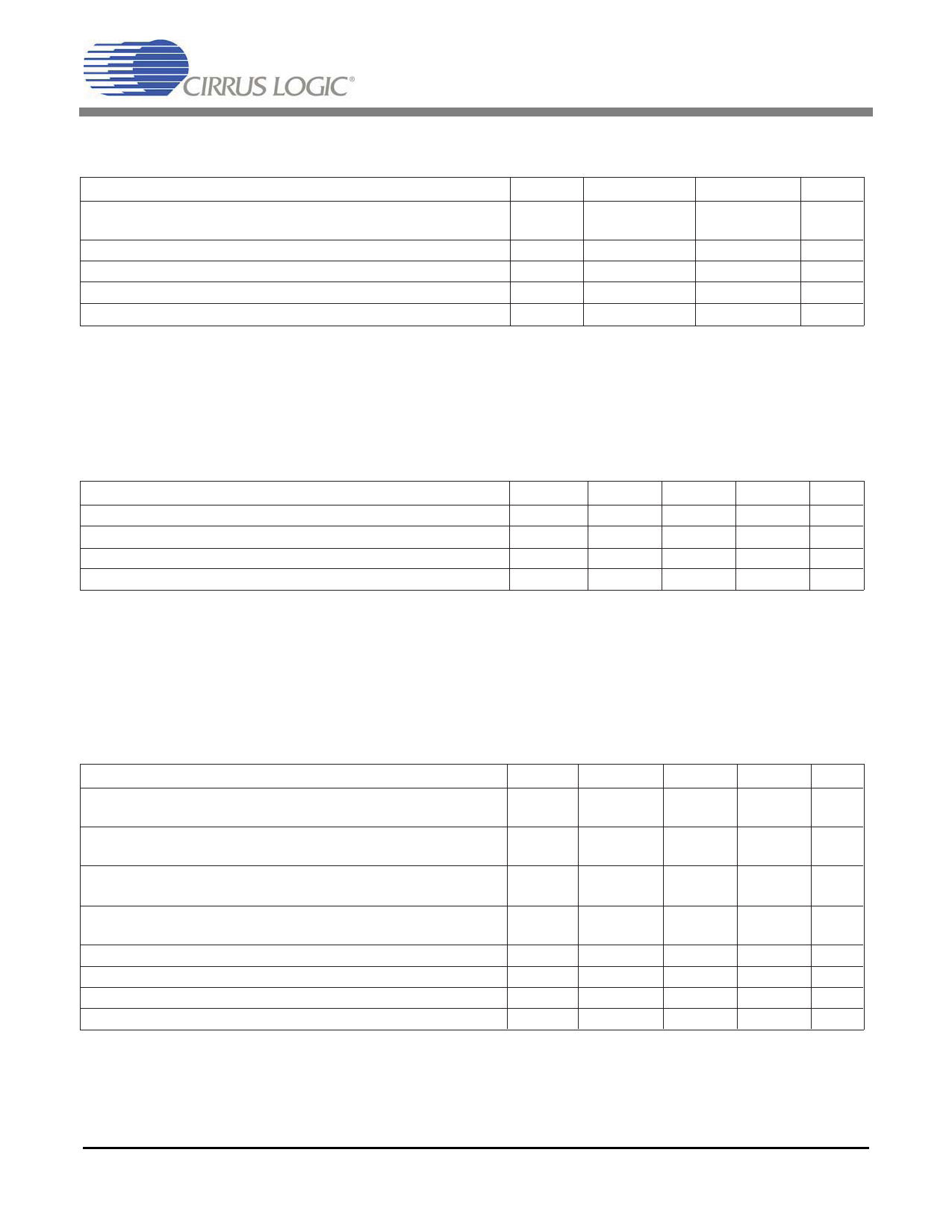

!"3/,54%�-!8)-5-�2!4).'3

0ARAMETER

3YMBOL

-IN

-AX

5NITS

DC Supply

(referenced to RGND=TGND=0V) RV+

TV+

-

6.0

V

-

(RV+) + 0.3 V

Input Voltage, Any Pin

Input Current, Any Pin

Ambient Operating Temperature

(Note 1) Vin

(Note 2) Iin

TA

RGND-0.3 (RV+) + 0.3 V

-10

10

mA

-40

85

°C

Storage Temperature

Tstg

-65

150

°C

WARNING:Operations at or beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

Notes: 1. Excluding RTIP, RRING, which must stay within -6V to (RV+) + 0.3V.

2. Transient currents of up to 100 mA will not cause SCR latch-up. Also TTIP, TRING, TV+ and TGND

can withstand a continuous current of 100 mA.

2%#/--%.$%$�/0%2!4).'�#/.$)4)/.3

0ARAMETER

3YMBOL -IN

4YP

-AX 5NITS

DC Supply

(Note 3) RV+, TV+ 4.75

5.0

5.25

V

Ambient Operating Temperature

TA

-40

25

85

°C

Power Consumption

(Notes 4,5) PC

-

400

500 mW

Power Consumption

(Notes 4,6) PC

-

230

-

mW

Notes: 3. TV+ must not exceed RV+ by more than 0.3V.

4. Power consumption while driving line load over operating temperature range. Includes IC and load.

Digital input levels are within 10% of the supply rails and digital outputs are driving a 50 pF

capacitive load.

5. Assumes 100% ones density and maximum line length at 5.25V.

6. Assumes 50% ones density and 300ft. line length at 5.0V.

$)')4!,�#(!2!#4%2)34)#3�� (TA = -40°C to 85°C; TV+, RV+ = 5.0V ±5%; GND = 0V)

0ARAMETER

3YMBOL -IN

4YP

-AX

High-Level Input Voltage

(Notes 7, 8) VIH

2.0

-

-

PINS 1-4, 17, 18, 23-28

Low-Level Input Voltage

(Notes 7, 8) VIL

-

PINS 1-4, 17, 18, 23-28

-

0.8

High-Level Output Voltage

(Notes 7, 8, 9) VOH

4.0

IOUT = -40 μA

PINS 6-8, 11, 12, 25

Low-Level Output Voltage

(Notes 7, 8, 9) VOL

-

IOUT = 1.6 mA

PINS 6-8, 11, 12, 23, 25

Input Leakage Current (Except Pin 5)

-

-

-

-

0.4

-

±10

Low-Level Input Voltage, PIN 5

VIL

-

-

0.2

High-Level Input Voltage, PIN 5

VIH (RV+) - 0.2 -

-

Mid-Level Input Voltage, PIN 5

(Note 10) VIM

2.3

-

2.7

Notes: 7. In Extended Hardware Mode, pins 17 and 18 are digital inputs. In Host Mode, pin 23 is

an open drain output and pin 25 is a tristate output.

8. This specification guarantees TTL compatibility (VOH = 2.4V @ IOUT = -40μA).

9. Output drivers will drive CMOS logic levels into a CMOS load.

10. As an alternative to supplying a 2.3-to-2.7V input, this pin may be left floating.

5NITS

V

V

V

V

μA

V

V

V

2

$3DS15050F