CS61584A データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

メーカー

CS61584A Datasheet PDF : 54 Pages

| |||

DS261PP5

CS61584A

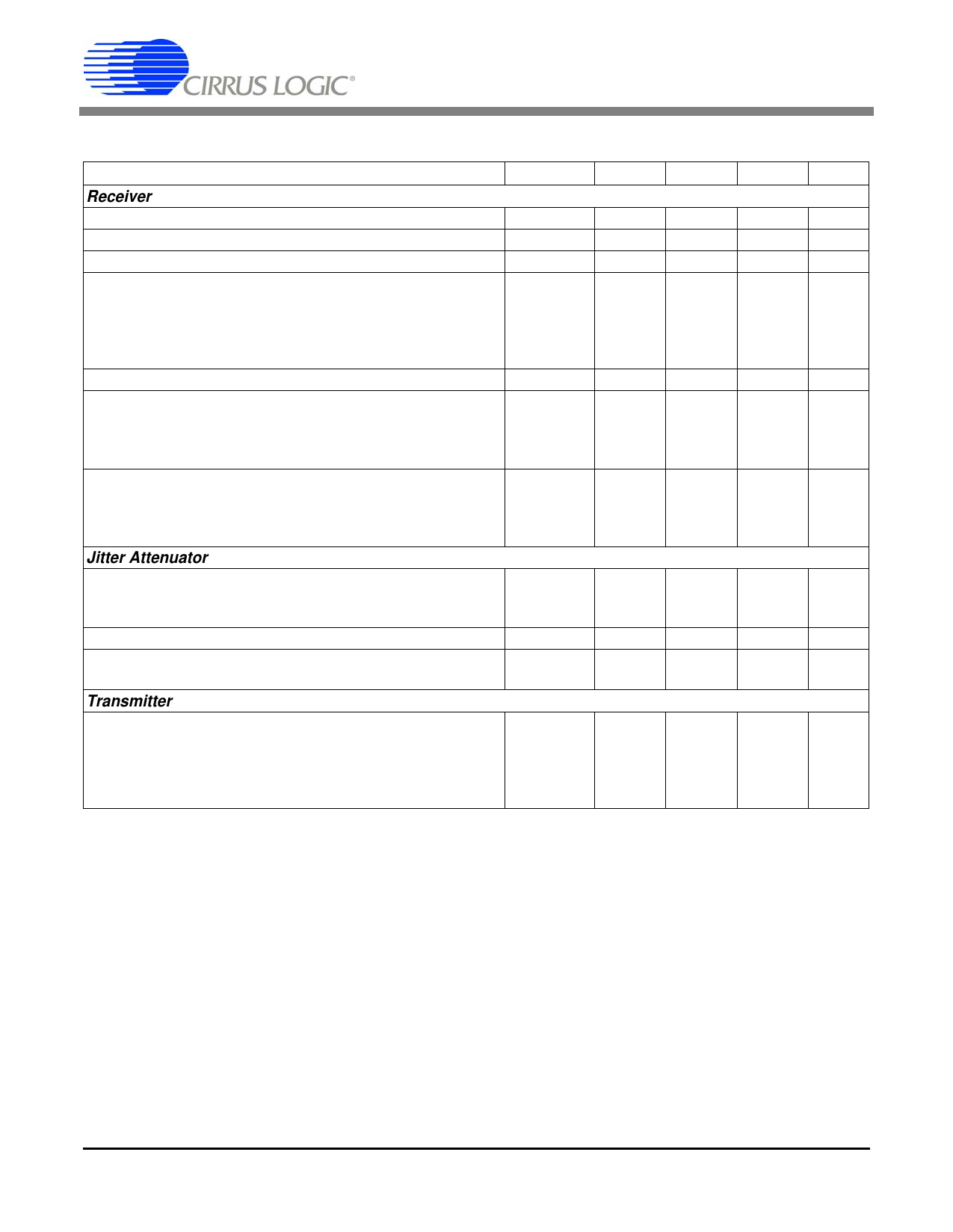

ANALOG CHARACTERISTICS (TA = -40 to 85 °C; power supply pins within ±5% of nominal.)

Parameter

Symbol Min

Typ

Max Unit

Receiver

RTIP/RRING Differential Input Impedance

-

20

-

kΩ

Sensitivity Below DSX-1 (0 dB = 2.4 V)

-

-13.6

-

dB

Loss of Signal Threshold

-

0.3

-

V

Data Decision Threshold

T1, DSX-1

(Note 7)

(Note 8)

T1, FCC Part 68 and E1 (Note

9)

(Note 10)

60

65

70

% of

55

-

75 Peak

45

50

55

40

-

60

Allowable Consecutive Zeros before LOS

160

175

190

bits

Receiver Input Jitter Tolerance (DSX-1, E1)

10 Hz and below

2 kHz

10 kHz - 100 kHz

(Note 11)

300

-

6.0

-

0.4

-

UI

-

-

-

Receiver Return Loss

(Notes 12, 13, and 14)

51 kHz - 102 kHz

102 kHz - 2.048 MHz

2.048 MHz - 3.072 MHz

12

22

18

24

14

22

dB

-

-

-

Jitter Attenuator

Jitter Attenuator Corner Frequency

Hz

T1

(Notes 12 and 15)

E1

1.25

4.0

-

-

1.25

-

Attenuation at 10 kHz Jitter Frequency (Notes 12 and 15)

-

60

-

dB

Attenuator Input Jitter Tolerance

(Note 12)

(Before Onset of FIFO Overflow or Underflow Protection)

28

43

-

UIpk-pk

Transmitter

Arbitrary Pulse Amplitude at Transformer Secondary

T1, DSX-1

T1, DS1

E1, 75 Ω

E1, 120 Ω

mV/LS

-

73

-

B

-

52

-

-

43

-

-

52

-

Notes: 7.

8.

9.

10.

11.

For input amplitude of 1.2 Vpk to 4.14 Vpk.

For input amplitude of 0.5 Vpk to 1.2 Vpk, and 4.14 Vpk to 5.0 Vpk.

For input amplitude of 1.07 Vpk to 4.14 Vpk.

For input amplitude of 4.14 Vpk to 5.0 Vpk.

Jitter tolerance increases at lower frequencies. Refer to the Receiver section.

12. Not production tested. Parameters guaranteed by design and characterization.

13. Typical performance using the line interface circuitry recommended in the Applications section.

14. Return loss = 20 log10 ABS((z1 + z0) / (z1 - z0)) where z1 = impedance of the transmitter or receiver, and

z0 = cable impedance.

15. Attenuation measured with sinusoidal input jitter equal to 3/4 of measured jitter tolerance. Circuit

attenuates jitter at 20 dB/decade above the corner frequency. Output jitter can increase significantly

when more than 28 UI's are input to the attenuator. The jitter attenuator -3 dB knee in T1 mode is

selectable for 4.0 Hz or 1.25 Hz. Refer to the Jitter Attenuator section.

6

DDS2S6216P1PF15