CY7B9910 データシートの表示(PDF) - Cypress Semiconductor

部品番号

コンポーネント説明

メーカー

CY7B9910 Datasheet PDF : 11 Pages

| |||

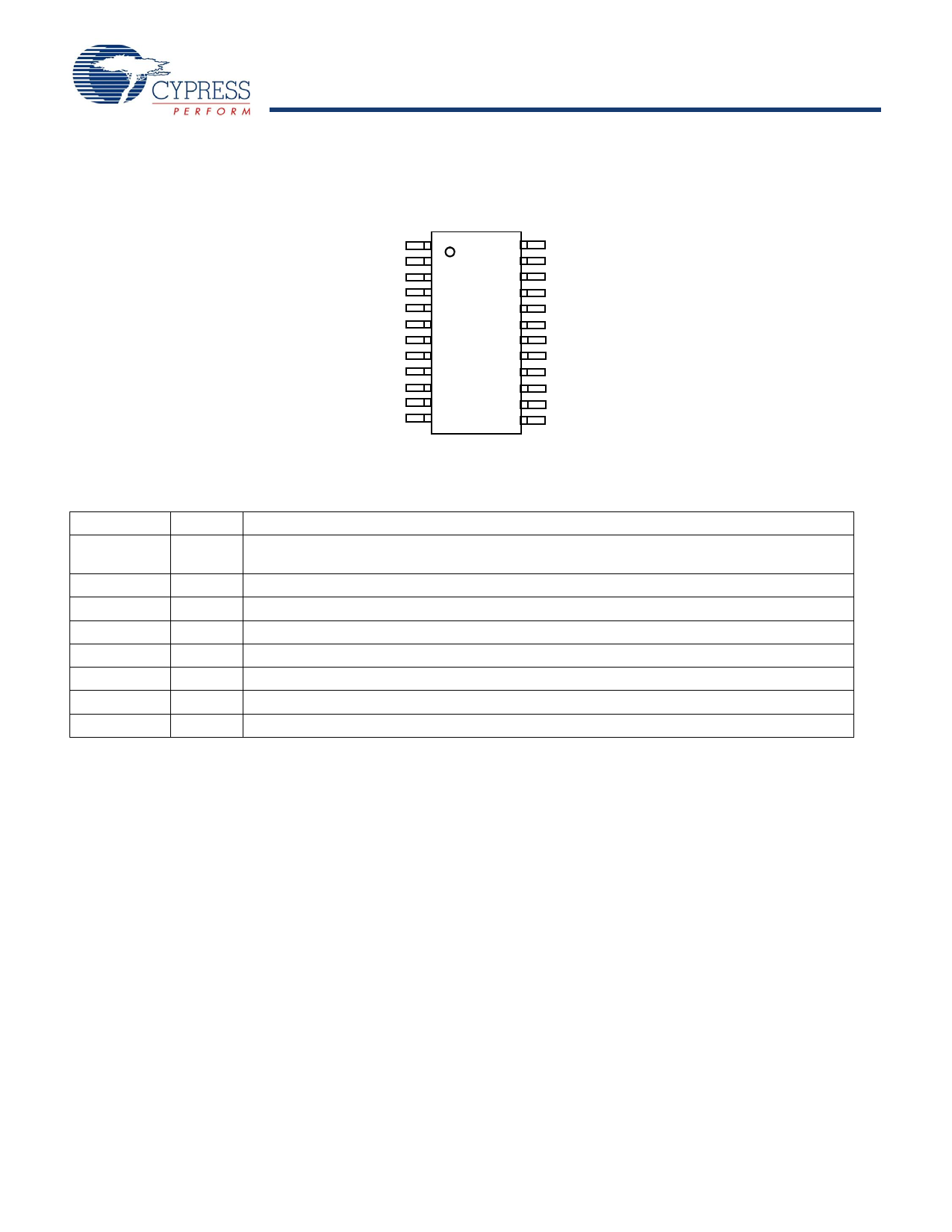

CY7B9910

CY7B9920

Pin Configuration

REF

VCCQ

FS

NC

VCCQ

VCCN

Q0

Q1

GND

Q2

Q3

VCCN

SOIC

Top View

1

24

2

23

3

22

4

21

5

20

6 7B9910 19

7 7B9920 18

8

17

9

16

10

15

11

14

12

13

GND

TEST

NC

GND

VCCN

Q7

Q6

GND

Q5

Q4

VCCN

FB

Pin Definitions

Signal Name

REF

FB

FS[1,2,3]

TEST

Q[0..7]

VCCN

VCCQ

GND

IO

I

I

I

I

O

PWR

PWR

PWR

Description

Reference frequency input.This input supplies the frequency and timing against which all functional

variations are measured.

PLL feedback input (typically connected to one of the eight outputs).

Three level frequency range select.

Three level select. See TEST MODE.

Clock outputs.

Power supply for output drivers.

Power supply for internal circuitry.

Ground.

Test Mode

The TEST input is a three level input. In normal system operation, this pin is connected to ground, allowing the CY7B9910 and

CY7B9920 to operate as described in Block Diagram Description. For testing purposes, any of the three level inputs can have a

removable jumper to ground or be tied LOW through a 100W resistor. This enables an external tester to change the state of these pins.

If the TEST input is forced to its MID or HIGH state, the device operates with its internal phase locked loop disconnected and input

levels supplied to REF directly control all outputs. Relative output-to-output functions are the same as in normal mode.

Notes

1. For all three state inputs, HIGH indicates a connection to VCC, LOW indicates a connection to GND, and MID indicates an open connection. Internal termination

circuitry holds an unconnected input to VCC/2.

2. The level to be set on FS is determined by the “normal” operating frequency (fNOM) of the VCO (see Logic Block Diagram). The frequency appearing at the REF

and FB inputs are fNOM when the output connected to FB is undivided. The frequency of the REF and FB inputs are fNOM/X when the device is configured for a

frequency multiplication by using external division in the feedback path of value X.

3. When the FS pin is selected HIGH, the REF input must not transition upon power up until VCC reached 4.3V.

Document Number: 38-07135 Rev. *B

Page 2 of 11

[+] Feedback