CY7B9910 データシートの表示(PDF) - Cypress Semiconductor

部品番号

コンポーネント説明

メーカー

CY7B9910 Datasheet PDF : 11 Pages

| |||

CY7B9910

CY7B9920

Capacitance

Tested initially and after any design or process changes that may affect these parameters.

Parameter

Description

Test Conditions

Max

Unit

CIN

Input Capacitance

TA = 25°C, f = 1 MHz, VCC = 5.0V

10

pF

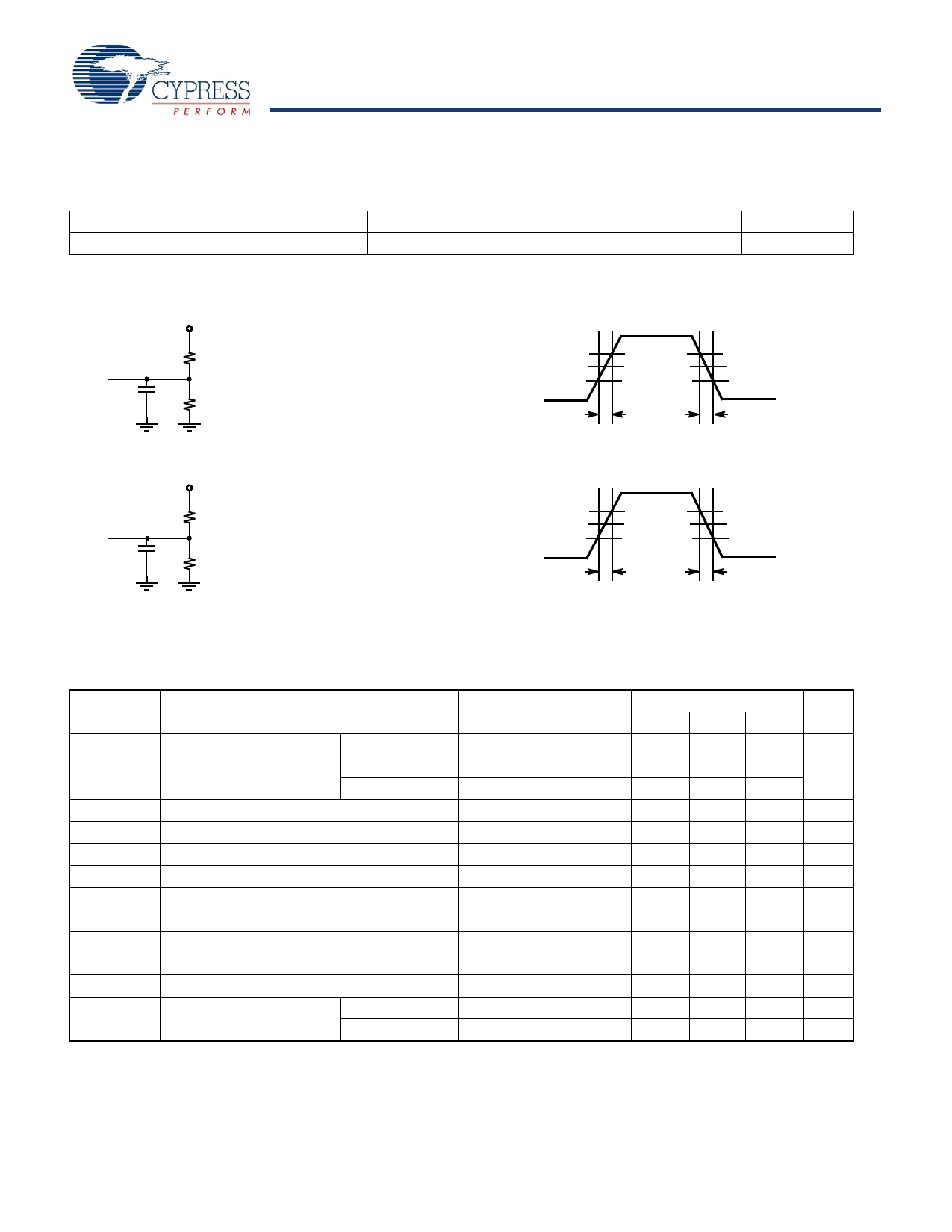

AC Test Loads and Waveforms

5V

R1 R1=130

R2=91

CL = 50 pF (CL = 30pF for –5 and – 2 devices)

CL

R2 (Includes fixture and probe capacitance)

7B9910–3

TTL AC Test Load (CY7B9910)

VCC

R1=100

R1

R2=100

CL = 50 pF (CL =30 pF for –5 and – 2devices)

(Includes fixture and probe capacitance)

CL

R2

7B9910–5

CMOS AC Test Load (CY7B9920)

Switching Characteristics

3.0V

2.0V

Vth =1.5V

0.8V

0.0V

2.0V

Vth =1.5V

0.8V

≤1ns

≤1ns

7B9910–4

TTL Input Test Waveform (Cy7B9910)

VCC

80%

Vth = VCC/2

20%

0.0V

80%

Vth = VCC/2

20%

≤ 3ns

≤ 3ns

7B9910–6

CMOS Input Test Waveform (CY7B9920)

Over the Operating Range [11]

Parameter

fNOM

tRPWH

tRPWL

tSKEW

tDEV

tPD

tODCV

tORISE

tOFALL

tLOCK

tJR

Description

Operating Clock

Frequency in MHz

FS = LOW[1, 2]

FS = MID[1, 2]

FS = HIGH[1, 2, 3]

REF Pulse Width HIGH

REF Pulse Width LOW

Zero Output Skew (All Outputs)[13, 14]

Device-to-Device Skew[14, 15]

Propagation Delay, REF Rise to FB Rise

Output Duty Cycle Variation[16]

Output Rise Time[17, 18]

Output Fall Time[17, 18]

PLL Lock Time[19]

Cycle-to-Cycle Output Jitter Peak to Peak

RMS

CY7B9910–2[8]

Min Typ Max

15

30

25

50

40

80

5.0

5.0

0.1 0.25

0.75

–0.25 0.0 +0.25

–0.65 0.0 +0.65

0.15 1.0 1.2

0.15 1.0 1.2

0.5

200

25

CY7B9920–2[8]

Min Typ Max

15

30

25

50

40

80[12]

5.0

5.0

0.1

0.25

0.75

–0.25 0.0

+0.25

–0.65 0.0

+0.65

0.5

2.0

2.5

0.5

2.0

2.5

0.5

200

25

Unit

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ms

ps

ps

Document Number: 38-07135 Rev. *B

Page 5 of 11

[+] Feedback