M59MR032C120ZC6T データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

M59MR032C120ZC6T

M59MR032C120ZC6T Datasheet PDF : 49 Pages

| |||

M59MR032C, M59MR032D

Auto Select (AS) Instruction. This instruc-

tion uses two Coded Cycles followed by one write

cycle giving the command 90h to address 555h for

command set-up. A subsequent read will output

the Manufacturer or the Device Code (Electronic

Signature), the Block Protection status or the Con-

figuration Register status depending on the levels

of ADQ0 and ADQ1 (see Tables 9, 10 and 11).

The Electronic Signature can be read from the

memory allowing programming equipment or ap-

plications to automatically match their interface to

the characteristics of M59MR032. The Manufac-

turer Code is output when the address lines ADQ0

and ADQ1 are at VIL, the Device Code is output

when ADQ0 is at VIH with ADQ1 at VIL.

The codes are output on ADQ0-ADQ7 with ADQ8-

ADQ15 at 00h. The AS instruction also allows the

access to the Block Protection Status. After giving

the AS instruction, ADQ0 is set to VIL with ADQ1

at VIH, while A12-A20 define the address of the

block to be verified (see Table 10). The AS Instruc-

tion finally allows the access to the Configuration

Register status if both ADQ0 and ADQ1 are set to

VIH; refer to Table 12 for configuration register de-

scription.

A reset command puts the device in Read Array

mode.

Write Configuration Register (CR) Instruc-

tion. This instruction uses two Coded Cycles fol-

lowed by one write cycle giving the command 60h

to address 555h. A further write cycle giving the

command 03h writes the contents of address bits

ADQ0-ADQ15 to bits CR15-CR0 of the configura-

tion register. At Power-up the Configuration Reg-

ister is set to asynchronous Read mode, Power-

down disabled and bus invert (power save func-

tion) disabled.

A description of the effects of each configuration

bit is given in Table 12.

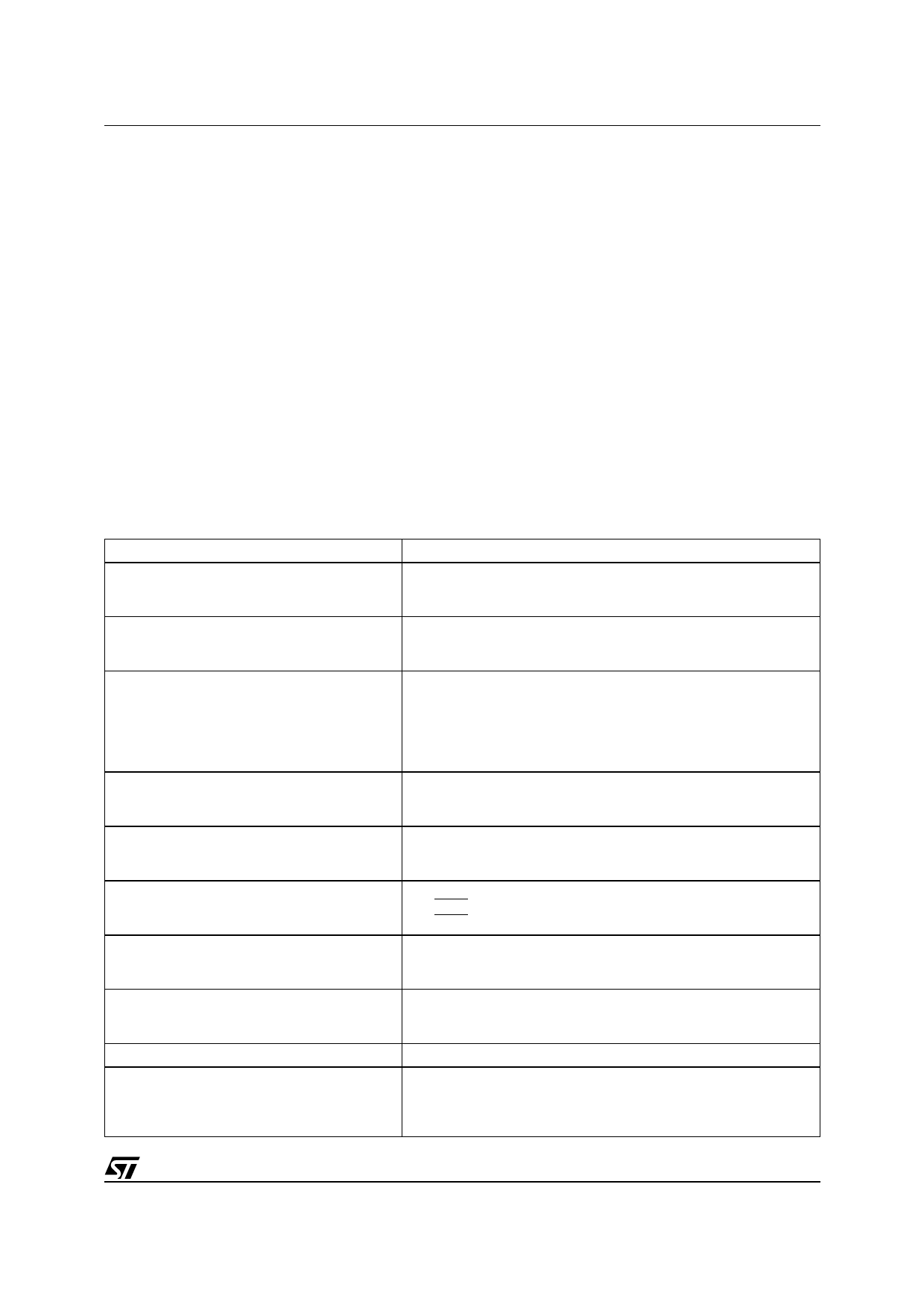

Table 12. Read Configuration Register (AS and Read CFI instructions)

Configuration Register

Function

CR15

Read mode

0 = Burst mode read

1 = Page mode read (default)

CR14

Bus Invert configuration (power save)

0 = disabled (default)

1 = enabled

CR13-CR11

X-Latency

010 = 2 clock latency

011 = 3 clock latency

100 = 4 clock latency

101 = 5 clock latency

110 = 6 clock latency

CR10

Power-down configuration

0 = power-down disabled (default)

1 = power-down enabled

CR9

Data hold configuration

0 = data output at every clock cycle

1 = data output every 2 clock cycles

CR8

Wait configuration

0 = WAIT is active during wait state

1 = WAIT is active one data cycle before wait state

CR7

Burst order configuration

0 = Interleaved

1 = Linear

CR6

Clock configuration

0 = Address latched and data output on the falling clock edge.

1 = Address latched and data output on the rising clock edge.

CR5-CR3

Reserved

CR2-CR0

Burst length

001 = 4 word burst length

010 = 8 word burst length

111 = Continuous burst mode (requires CR7 = 1)

13/49